IC 검증 및 유효성 검사와 관련된 비용은 설계 비용 보다 매우 빠르게 증가하고 있다. SoC 소프트웨어 검증 비용은 소프트웨어와 하드웨어에서 모두 빠르게 증가하고 있으며, 특히 하드웨어 검증 비용은 RTL 시뮬레이션 보다 빠르게 증가하고 있다. 2018년 4분기에는 하드웨어 검증 비용에 대한 지출이 사실상 처음으로 RTL 시뮬레이션 지출을 초과했으며, 이러한 추세는 계속되고 있다.

반도체의 성공을 결정하는 요인은 이제 소프트웨어 성능에 의해 좌우된다고 해도 과언이 아니다. 이전에는 성공적인 반도체의 기준은 주로 하드웨어의 기능 사양에 주목했지만, 이제는 성능 분석 소프트웨어를 이용하여 작업부하와 프레임워크를 실행하고, 수많은 시장별로 특화된 벤치마크도 실행해야 한다. 소프트웨어 작업부하와 벤치마크를 이용해 전력과 성능을 검증하는 것이 가장 중요한 핵심 사항이 되었다. 따라서 이러한 다양한 작업부하 및 벤치마크 요건을 충족시키기 위해서는 하드웨어 기반 검증 환경이 필요하다.

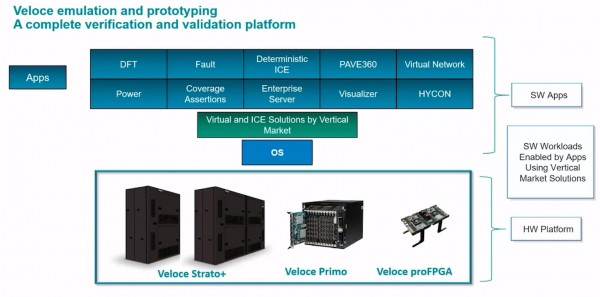

지멘스 EDA 코리아 이정현 상무는 “벨로체는 에뮬레이션 플랫폼과 FPGA 플랫폼을 통합한 검증 시스템으로 3개의 다른 하드웨어가 동일 소프트웨어에서 실행되는 장점을 가지고 있다. 특히 업계에서는 처음으로 FPGA 플랫폼과 에뮬레이션 플랫폼을 단일 플랫폼으로 실행할 수 있어 차세대 IC 설계 검증작업을 획기적으로 혁신할 수 있게 되었다.”고 밝혔다.

지멘스 디지털 인더스트리 소프트웨어, 지멘스 EDA 사업부는 고도로 정교한 차세대 IC 디자인의 신속한 검증을 위한 벨로체(Veloce) 하드웨어 기반 검증 시스템을 발표했다. 이 시스템은 동급 최고의 가상 플랫폼과 하드웨어 에뮬레이션 및 FPGA(Field Programmable Gate Array) 프로토타이핑 기술을 최초로 결합시킨 완벽한 통합 제품으로서 강력한 최신 하드웨어 기반 검증 방법을 활용할 수 있도록 해준다.

지멘스 EDA 코리아 이정현 상무는 “벨로체는 에뮬레이션 플랫폼과 FPGA 플랫폼을 통합한 검증 시스템으로 3개의 다른 하드웨어가 동일 소프트웨어에서 실행되는 장점을 가지고 있다. 특히 업계에서는 처음으로 FPGA 플랫폼과 에뮬레이션 플랫폼을 단일 플랫폼으로 실행할 수 있어 차세대 IC 설계 검증작업을 획기적으로 혁신할 수 있게 되었다.”고 밝혔다.

가상 플랫폼 및 소프트웨어 지원 검증을 위한 벨로체 HYCON(HYbrid CONfigurable) 차세대 SoC 디자인을 위한 복합형 하이브리드 에뮬레이션 시스템을 개발할 수 있다. 벨로체 Strato+는 최대 150억 게이트까지 확장 가능한 업계 최고의 용량 로드맵을 갖추고 있으며, 업계 최고의 총 처리 속도와 가장 빠른 통합 모델링 대역폭 및 가시성 확보 시간(TTV: time-to-visibility)을 제공한다. 엔터프라이즈 레벨의 FPGA 프로토타이핑을 위한 벨로체 Primo는 업계 최고의 런타임 성능과 매우 빠른 프로토타입 브링업 속도를 결합시킨 자체 개발 엔터프라이즈 프로토타이핑 솔루션이다. 데스크탑 FPGA 프로토타이핑을 위한 벨로체 proFPGA는 모듈식 용량 접근 방식을 통해 다양한 분야에 걸쳐 확장성을 제공한다.

차세대 IC 디자인의 신속한 검증을 위한 벨로체(Veloce) 하드웨어 지원 검증 시스템은 가상 플랫폼과 하드웨어 에뮬레이션 및 FPGA 프로토타이핑 기술을 최초로 결합시킨 완벽한 통합 제품으로서 강력한 최신 하드웨어 지원 검증 방법을 활용할 수 있도록 해준다.

이러한 솔루션은 통합 플랫폼 형태로 사용할 수 있어 하드웨어 지원 검증 방법론이 향후 나아갈 방향에 대한 새로운 표준을 세우고 있다. 이 시스템은 검증 주기를 간소화하고 최적화하는 동시에 검증 비용도 절감할 수 있도록 지원함으로써 하드웨어, 소프트웨어 및 시스템 검증에 대한 새로운 차원의 대안을 제시하고 있다.

이는 검증주기 관리를 위한 완벽한 접근 방식으로서, 특정 시장의 실제 작업부하, 프레임워크 및 벤치마크를 전력 및 성능 분석을 위한 검증 주기 초기에 실행하는 데 역점을 두고 있다. 이를 통해 고객은 사이클 초기에 가상 SoC 모델을 제작하고 통합하여 실제 펌웨어 및 소프트웨어를 벨로체 Strato+에서 실행하기 시작함으로써 최하위 수준의 하드웨어에 대한 심층적인 가시성을 확보할 수 있다.

그런 다음 동일한 설계를 벨로체 Primo로 옮겨 소프트웨어 및 하드웨어 인터페이스를 검증하고 애플리케이션 레벨 소프트웨어를 좀 더 실제에 가까운 시스템 속도로 실행할 수 있다. 이러한 접근 방식을 보다 효율적으로 만들기 위해 벨로체 Strato+와 벨로체 Primo는 동일한 RTL과 동일한 가상 검증 환경, 동일한 트랜잭터 및 모델을 사용함으로써 검증 부수자료, 환경 및 테스트 콘텐츠의 재사용을 극대화한다.

진선옥 기자 (jadejin@all4chip.com)

저작권©올포칩 미디어. 무단전재 및 재배포를 금지합니다.

깃랩, 제5차 연간 글로벌 데브섹옵스 설문조사 결과 발표2021년 설문조사 결과에 따르면, 코로나 19 대유행으로 인해 원격근무가 광범위하게 채택되면서 팀이 쿠버네티스(Kubernetes)와 머신러닝/인공지능 및 클라우드 컴퓨팅과 같은 최첨단 데브옵스 기술 도입을 적극적으로 수용한 것으로 나타났다. 지난해는 데브옵스의 성장과 이러한 기술 채택이 성숙단계에 이르렀지만, 진정한 데브섹옵스를 달성하기 위해서는 여전히 처리해야 할 장애물들이 남아 있는 것으로 확인되었다.

깃랩, 제5차 연간 글로벌 데브섹옵스 설문조사 결과 발표2021년 설문조사 결과에 따르면, 코로나 19 대유행으로 인해 원격근무가 광범위하게 채택되면서 팀이 쿠버네티스(Kubernetes)와 머신러닝/인공지능 및 클라우드 컴퓨팅과 같은 최첨단 데브옵스 기술 도입을 적극적으로 수용한 것으로 나타났다. 지난해는 데브옵스의 성장과 이러한 기술 채택이 성숙단계에 이르렀지만, 진정한 데브섹옵스를 달성하기 위해서는 여전히 처리해야 할 장애물들이 남아 있는 것으로 확인되었다. 마이크로소프트, 최대 개발자 대회 ‘빌드 2021’ 온라인 개최 임박매년 5월 열리는 마이크로소프트 빌드는 개발자와 아키텍트는 물론 스타트업과 학생 등이 만나 지식을 공유하고, 기술력을 확장하는 동시에 새로운 미래 혁신 방법을 모색하는 행사다. 특히 올해는 기업의 기술 역량이 커지면서 애플리케이션 개발 방식과 개발자의 역할이 변화함에 따라, 마이크로소프트는 인류 문제 해결과 경제 회복에 큰 역할을 하게 될 개발자들을 지원하기 위한 다양한 기술과 도구를 대거 공개할 예정이다.

마이크로소프트, 최대 개발자 대회 ‘빌드 2021’ 온라인 개최 임박매년 5월 열리는 마이크로소프트 빌드는 개발자와 아키텍트는 물론 스타트업과 학생 등이 만나 지식을 공유하고, 기술력을 확장하는 동시에 새로운 미래 혁신 방법을 모색하는 행사다. 특히 올해는 기업의 기술 역량이 커지면서 애플리케이션 개발 방식과 개발자의 역할이 변화함에 따라, 마이크로소프트는 인류 문제 해결과 경제 회복에 큰 역할을 하게 될 개발자들을 지원하기 위한 다양한 기술과 도구를 대거 공개할 예정이다. 온세미컨덕터, 보쉬 IoT 스위트에 자사 플랫폼 통합현재 RSL10 센서 개발키트와 RSL10 스마트샷 카메라가 보쉬 IoT 스위트 생태계 내에서 지원되고 있으며, 향후 더 많은 플랫폼이 추가될 전망이다. IoT로 자동화되고 지능화된 인프라가 구현되면서 일상생활과 업무환경 모든 측면에서 다양한 기회가 창출되고 있다. 또한, 많은 신생 기업들은 가까운 미래에 더 향상된 기능을 제공할 혁신적인 아이디어와 솔루션을 선보이며 IoT 시장에 진출하고 있다.

온세미컨덕터, 보쉬 IoT 스위트에 자사 플랫폼 통합현재 RSL10 센서 개발키트와 RSL10 스마트샷 카메라가 보쉬 IoT 스위트 생태계 내에서 지원되고 있으며, 향후 더 많은 플랫폼이 추가될 전망이다. IoT로 자동화되고 지능화된 인프라가 구현되면서 일상생활과 업무환경 모든 측면에서 다양한 기회가 창출되고 있다. 또한, 많은 신생 기업들은 가까운 미래에 더 향상된 기능을 제공할 혁신적인 아이디어와 솔루션을 선보이며 IoT 시장에 진출하고 있다. 맥스트, 과기부 주관 디지털뉴딜 사업 ‘XR 메타버스 프로젝트’ 주관사 선정이번 프로젝트를 위해 구성된 콘소시엄은 맥스트가 주관사를 맡고 XR 분야의 전문 기술 기업들이 참여했다. ① 서비스 콘텐츠 개발 분야에는 위즈윅스튜디오, 스페이스엘비스, 렛시 ② 메타버스 플랫폼 개발 분야에는 맥스트, 알파서클 ③ AR글래스 개발 분야에는 레티널, 파노비젼 ④ 품질 인증 및 시험 분야에는 구미전자정보기술원으로 구성되어 있다.

맥스트, 과기부 주관 디지털뉴딜 사업 ‘XR 메타버스 프로젝트’ 주관사 선정이번 프로젝트를 위해 구성된 콘소시엄은 맥스트가 주관사를 맡고 XR 분야의 전문 기술 기업들이 참여했다. ① 서비스 콘텐츠 개발 분야에는 위즈윅스튜디오, 스페이스엘비스, 렛시 ② 메타버스 플랫폼 개발 분야에는 맥스트, 알파서클 ③ AR글래스 개발 분야에는 레티널, 파노비젼 ④ 품질 인증 및 시험 분야에는 구미전자정보기술원으로 구성되어 있다. 포스트 무어의 시대를 선도하는 자일링스의 성장 전략디지털화의 가속과 커넥티드 및 스마트 세계로의 확장을 위한 혁신 속도가 갈수록 빨라지면서 무어의 법칙을 넘어서는 새로운 전략이 필요하게 되었다. 자일링스(Xilinx)는 포스트 무어의 시대를 선도하는 자사의 신성장 동력으로 적응형 컴퓨팅 전략을 수립하고 시장 확장에 주력하고 있다. 기존의 FPGA 제품군과 적응형 SoC 및 ACAP(적응형 및 지능형 컴퓨팅 플랫폼)을 기반으로 한 자일링스의 신성장 전략은 자동차를 비롯한 산업, 비전, 헬스케어, 과학, 항공우주 및 방위 분야에서 지난 3년 동안 평균 9%의 높은 성장률을 기록하며, 성과를 거두고 있다.

포스트 무어의 시대를 선도하는 자일링스의 성장 전략디지털화의 가속과 커넥티드 및 스마트 세계로의 확장을 위한 혁신 속도가 갈수록 빨라지면서 무어의 법칙을 넘어서는 새로운 전략이 필요하게 되었다. 자일링스(Xilinx)는 포스트 무어의 시대를 선도하는 자사의 신성장 동력으로 적응형 컴퓨팅 전략을 수립하고 시장 확장에 주력하고 있다. 기존의 FPGA 제품군과 적응형 SoC 및 ACAP(적응형 및 지능형 컴퓨팅 플랫폼)을 기반으로 한 자일링스의 신성장 전략은 자동차를 비롯한 산업, 비전, 헬스케어, 과학, 항공우주 및 방위 분야에서 지난 3년 동안 평균 9%의 높은 성장률을 기록하며, 성과를 거두고 있다. 인텔, 새로운 11세대 코어 모바일 프로세서 출시11세대 인텔 코어 H 시리즈 프로세서는 모바일 게임, 콘텐츠 제작, 상용 워크스테이션 시스템 성능을 한 단계 끌어올렸다. 새로운 H 시리즈 프로세서는 모바일 제품군의 확장 버전으로, 단일 코어 및 멀티 코어의 성능을 두 자릿수로 향상했다. 또한, 업계 최고의 게임 플레이 성능, 직접 연결 스토리지를 제공하고, 마니아 수준의 플랫폼 대역폭을 위한 20개의 PCIe 4.0 레인으로 구성됐다

인텔, 새로운 11세대 코어 모바일 프로세서 출시11세대 인텔 코어 H 시리즈 프로세서는 모바일 게임, 콘텐츠 제작, 상용 워크스테이션 시스템 성능을 한 단계 끌어올렸다. 새로운 H 시리즈 프로세서는 모바일 제품군의 확장 버전으로, 단일 코어 및 멀티 코어의 성능을 두 자릿수로 향상했다. 또한, 업계 최고의 게임 플레이 성능, 직접 연결 스토리지를 제공하고, 마니아 수준의 플랫폼 대역폭을 위한 20개의 PCIe 4.0 레인으로 구성됐다 에이디링크, 엔비디아 Turing 아키텍처 기반 임베디드 MXM 그래픽 모듈 출시에이디링크의 임베디드 MXM 그래픽 모듈은 수많은 컴퓨팅 집약적 애플리케이션, 특히 환경적으로 어려운 애플리케이션에서 엣지 컴퓨팅과 엣지 AI를 가속화한다. 예로는 의료 영상, 산업 자동화, 생체인식 접근 제어, 자율 모바일 로봇, 운송 및 항공 우주 및 방어가 포함된다. 엣지의 AI가 보편화됨에 따라 고성능, 저전력 GPU 모듈에 대한 필요성이 점점 더 중요해지고 있다.

에이디링크, 엔비디아 Turing 아키텍처 기반 임베디드 MXM 그래픽 모듈 출시에이디링크의 임베디드 MXM 그래픽 모듈은 수많은 컴퓨팅 집약적 애플리케이션, 특히 환경적으로 어려운 애플리케이션에서 엣지 컴퓨팅과 엣지 AI를 가속화한다. 예로는 의료 영상, 산업 자동화, 생체인식 접근 제어, 자율 모바일 로봇, 운송 및 항공 우주 및 방어가 포함된다. 엣지의 AI가 보편화됨에 따라 고성능, 저전력 GPU 모듈에 대한 필요성이 점점 더 중요해지고 있다. 래티스, 차세대 산업 자동화 시스템을 위한 ‘오토메이트’ 솔루션 스택 발표산업 자동화 및 스마트 팩토리에 대한 요구가 확산되면서 다양한 애플리케이션 분야에서 자동화 시스템 구축이 활발히 전개되고 있다. 시장조사기관의 자료에 따르면 전 세계 산업 자동화 시장 규모는 2027 년까지 3,261억 달러 규모로 성장하고, 로보틱스 시장은 2020년에서 2027년까지 연평균 13.5%의 성장이 예상되고 있다. 차세대 자동화 시스템을 위해 향상된 정밀 모터 제어 기능과 예지정비, 실시간 네트워킹 및 사이버 레질런시 등이 요구되고 있으며, 이를 위해서는 저전력의 짧은 지연시간과 균일한 성능, 높은 신뢰성 및 각기 다른 통신 프로토콜을 지원할 수 있는 인터페이스 유연성을 갖춘 솔루션이 필요하다.

래티스, 차세대 산업 자동화 시스템을 위한 ‘오토메이트’ 솔루션 스택 발표산업 자동화 및 스마트 팩토리에 대한 요구가 확산되면서 다양한 애플리케이션 분야에서 자동화 시스템 구축이 활발히 전개되고 있다. 시장조사기관의 자료에 따르면 전 세계 산업 자동화 시장 규모는 2027 년까지 3,261억 달러 규모로 성장하고, 로보틱스 시장은 2020년에서 2027년까지 연평균 13.5%의 성장이 예상되고 있다. 차세대 자동화 시스템을 위해 향상된 정밀 모터 제어 기능과 예지정비, 실시간 네트워킹 및 사이버 레질런시 등이 요구되고 있으며, 이를 위해서는 저전력의 짧은 지연시간과 균일한 성능, 높은 신뢰성 및 각기 다른 통신 프로토콜을 지원할 수 있는 인터페이스 유연성을 갖춘 솔루션이 필요하다. 엔비디아-모두의연구소, ‘젯슨 AI 교육 프로그램’ 통해 차세대 AI 전문가 양성모두의연구소 인천 캠퍼스 참가자는 엔비디아 젯슨 AI 교육 프로그램을 통해 6개월 동안 사물지능 산업에 맞는 차세대 AI 전문가로 성장할 기회를 얻게 된다. 또한, 참가자에게는 젯슨 나노(Jetson Nano) 2GB 개발자 키트가 무료 지원되며, 이를 바탕으로 한국어 교육 과정, 튜토리얼 및 오픈소스 프로젝트를 수행하며 효과적으로 AI 기술을 학습할 수 있다.

엔비디아-모두의연구소, ‘젯슨 AI 교육 프로그램’ 통해 차세대 AI 전문가 양성모두의연구소 인천 캠퍼스 참가자는 엔비디아 젯슨 AI 교육 프로그램을 통해 6개월 동안 사물지능 산업에 맞는 차세대 AI 전문가로 성장할 기회를 얻게 된다. 또한, 참가자에게는 젯슨 나노(Jetson Nano) 2GB 개발자 키트가 무료 지원되며, 이를 바탕으로 한국어 교육 과정, 튜토리얼 및 오픈소스 프로젝트를 수행하며 효과적으로 AI 기술을 학습할 수 있다. 유니버설 로봇, 스마트 팩토리를 위한 제조혁신, 그 중심에 있는 협동로봇정보통신기술(ICT)의 융합체로 불리우며, 4차산업혁명의 핵심으로 주목받고 있는 스마트 팩토리는 전 세계적으로 많은 기업들이 도입 중에 있다. 이러한 흐름에 맞춰 정부의 스마트 팩토리 지원사업은 활발하게 진행중이며, 로봇 산업 정책 자금 또한 크게 늘었다. 국내 기업들도 스마트 팩토리로의 전환을 고려하거나 계획 중에 있어, 전 세계가 스마트 팩토리 도입을 위해 빠르게 대처하고 있다는 것을 확인할 수 있다.

유니버설 로봇, 스마트 팩토리를 위한 제조혁신, 그 중심에 있는 협동로봇정보통신기술(ICT)의 융합체로 불리우며, 4차산업혁명의 핵심으로 주목받고 있는 스마트 팩토리는 전 세계적으로 많은 기업들이 도입 중에 있다. 이러한 흐름에 맞춰 정부의 스마트 팩토리 지원사업은 활발하게 진행중이며, 로봇 산업 정책 자금 또한 크게 늘었다. 국내 기업들도 스마트 팩토리로의 전환을 고려하거나 계획 중에 있어, 전 세계가 스마트 팩토리 도입을 위해 빠르게 대처하고 있다는 것을 확인할 수 있다. 깃랩, 연간 원격근무 보고서 발간: 새로운 변화의 시작올해의 보고서는 원격근무에 대한 포괄적인 내용을 다루고 있으며, 6개 대륙에 걸쳐 3,900명 이상이 설문조사에 참여했다. 코로나 대유행으로 인해 많은 기업들은 점차 진화하고 있는 업무공간의 유연성에 대한 기대치를 지원하기 위해 워크플로우와 문화를 새롭게 재구성해야 할 시점에 이르렀다. 2021 원격근무 보고서는 이러한 관점을 뒷받침하고, 원격근무를 확장하는 방법과 당면 과제 및 향후 전개 방향 등을 다루고 있다.

깃랩, 연간 원격근무 보고서 발간: 새로운 변화의 시작올해의 보고서는 원격근무에 대한 포괄적인 내용을 다루고 있으며, 6개 대륙에 걸쳐 3,900명 이상이 설문조사에 참여했다. 코로나 대유행으로 인해 많은 기업들은 점차 진화하고 있는 업무공간의 유연성에 대한 기대치를 지원하기 위해 워크플로우와 문화를 새롭게 재구성해야 할 시점에 이르렀다. 2021 원격근무 보고서는 이러한 관점을 뒷받침하고, 원격근무를 확장하는 방법과 당면 과제 및 향후 전개 방향 등을 다루고 있다. 미 우편국, 엔비디아 기반 엣지 AI 시스템 구축USPS AI 설계자인 라이언 심슨(Ryan Simpson)은 내부에서 개발하고 있던 이미지 분석 시스템을 훨씬 더 광범위하게 확장하고자 했다. 데이터 사이언티스트, 엔비디아 설계자 6명 등을 포함한 작업자들이 3주 동안 딥 러닝 모델을 빠르게 설계했다. 이 작업을 통해 엔비디아 EGX 플랫폼으로 가동되고 있는 분산형 엣지 AI 시스템인 엣지 컴퓨팅 인프라 프로그램(ECIP)을 구축했다.

미 우편국, 엔비디아 기반 엣지 AI 시스템 구축USPS AI 설계자인 라이언 심슨(Ryan Simpson)은 내부에서 개발하고 있던 이미지 분석 시스템을 훨씬 더 광범위하게 확장하고자 했다. 데이터 사이언티스트, 엔비디아 설계자 6명 등을 포함한 작업자들이 3주 동안 딥 러닝 모델을 빠르게 설계했다. 이 작업을 통해 엔비디아 EGX 플랫폼으로 가동되고 있는 분산형 엣지 AI 시스템인 엣지 컴퓨팅 인프라 프로그램(ECIP)을 구축했다. 인텔코리아, 코로나19 대응 기술 이니셔티브 국내 사례 공유1주년을 맞이한 PRTI는 의료, 교육, 경제 회복이라는 세 가지 영역에서 발생하는 문제를 해결하는데 초점을 맞췄으며, 세 영역의 취약점과 비효율을 타파하는 다각적 문제 해결을 통해 영향력을 극대화했다. 인텔은 프로젝트를 통해 가장 필요한 곳에 우선적으로 지원하고, 코로나19로 인한 뉴노멀에 맞는 혁신적인 솔루션을 개발하며, 미래 위기를 극복하는 기술에 투자했다.

인텔코리아, 코로나19 대응 기술 이니셔티브 국내 사례 공유1주년을 맞이한 PRTI는 의료, 교육, 경제 회복이라는 세 가지 영역에서 발생하는 문제를 해결하는데 초점을 맞췄으며, 세 영역의 취약점과 비효율을 타파하는 다각적 문제 해결을 통해 영향력을 극대화했다. 인텔은 프로젝트를 통해 가장 필요한 곳에 우선적으로 지원하고, 코로나19로 인한 뉴노멀에 맞는 혁신적인 솔루션을 개발하며, 미래 위기를 극복하는 기술에 투자했다. 다쏘시스템 등 5개 유럽 기업, ‘소프트웨어 리퍼블리크’ 설립자동차 및 IT 기술 업계를 선도하는 5개 기업의 인공지능(AI), 사이버보안, 커넥티드 기술, 임베디드 전자제품, 버추얼 트윈 기술은 신제품 및 신규 서비스 개발에 크게 기여할 것으로 전망된다. 또한, 개방형 혁신 생태계를 통해 새로운 구성원의 가입을 도모하며, 개방형 협업을 전개할 계획이다.

다쏘시스템 등 5개 유럽 기업, ‘소프트웨어 리퍼블리크’ 설립자동차 및 IT 기술 업계를 선도하는 5개 기업의 인공지능(AI), 사이버보안, 커넥티드 기술, 임베디드 전자제품, 버추얼 트윈 기술은 신제품 및 신규 서비스 개발에 크게 기여할 것으로 전망된다. 또한, 개방형 혁신 생태계를 통해 새로운 구성원의 가입을 도모하며, 개방형 협업을 전개할 계획이다.

ST, 집약적 움직임 분석 지원하는 관성 모듈로 엣지-AI 센서 제품군 확장

ST, 집약적 움직임 분석 지원하는 관성 모듈로 엣지-AI 센서 제품군 확장 HMS 네트웍스, AGV를 위한 첨단 무선 기술 지원

HMS 네트웍스, AGV를 위한 첨단 무선 기술 지원 리미니스트리트 ‘2024 리미니스트리트 써밋’, 엔터프라이즈 소프트웨어 유지보수 혁신 지원

리미니스트리트 ‘2024 리미니스트리트 써밋’, 엔터프라이즈 소프트웨어 유지보수 혁신 지원 마우저, IoT 및 에너지 하베스팅 설계 세미나 개최

마우저, IoT 및 에너지 하베스팅 설계 세미나 개최 매스웍스코리아, 다양한 분야의 AI 인재 발굴 위한 ‘제4회 매트랩 대학생 AI 경진대회’ 개최

매스웍스코리아, 다양한 분야의 AI 인재 발굴 위한 ‘제4회 매트랩 대학생 AI 경진대회’ 개최

- 다쏘시스템과 HD현대중공업, 버추얼 트윈 기반 설계-생산 일관화 통합 플랫폼 구축

- ams OSRAM과 도미넌트 옵토 테크놀로지스, 지능형 RGB LED로 스마트 자동차 실내 조명 구현

- 원프레딕트, 산업 AI 설비관리 솔루션으로 국제전기전력전시회 참가

- 에이디링크, 인텔 Amston-Lake 기반 모듈 출시

- 자이스 코리아, 제약바이오 연구 혁신을 지원하는 최신 고품질 이미징 기술 공개

- KT, K-UAM 실증서 세계 최초 UAM 통합운용체계 검증

그래픽 / 영상

인터넷의 ‘필터 버블(Filter Bubble)’ 깨부수기

인터넷의 ‘필터 버블(Filter Bubble)’ 깨부수기 결정론, 새로운 이더넷 애플리케이션을 열다

결정론, 새로운 이더넷 애플리케이션을 열다 AMD, 새로운 2세대 버설 적응형 SoC로 AI 기반 임베디드 시스템의 종단간 가속 지원

AMD, 새로운 2세대 버설 적응형 SoC로 AI 기반 임베디드 시스템의 종단간 가속 지원

많이 본 뉴스

버티브, 김성엽 신임 한국 사장 선임

버티브, 김성엽 신임 한국 사장 선임 전 세계 기업의 63%, 제로 트러스트 전략 도입할 방침

전 세계 기업의 63%, 제로 트러스트 전략 도입할 방침 원프레딕트, SFAW 2024에서 한국산업 디지털 전환 기여

원프레딕트, SFAW 2024에서 한국산업 디지털 전환 기여 ST, 지능형 기능과 효율성 결합한 하이사이드 스위치 출시

ST, 지능형 기능과 효율성 결합한 하이사이드 스위치 출시 한국 리미니스트리트, ‘대한민국 일하기 좋은 100대 기업’ 8위 선정

한국 리미니스트리트, ‘대한민국 일하기 좋은 100대 기업’ 8위 선정 로데슈바르즈, NTN NB-IoT 테스트 케이스의 신규 GCF 인증 획득

로데슈바르즈, NTN NB-IoT 테스트 케이스의 신규 GCF 인증 획득 레노버, AI PC 혁신의 미래 제시

레노버, AI PC 혁신의 미래 제시 로지텍, 플래그십 무선 게이밍 헤드셋 ‘A50 X’ 출시

로지텍, 플래그십 무선 게이밍 헤드셋 ‘A50 X’ 출시 하이크비전, 동원로엑스냉장투에 스마트 물류센터 위한 AI 솔루션 구축

하이크비전, 동원로엑스냉장투에 스마트 물류센터 위한 AI 솔루션 구축 TI, 임베디드 월드2024에서 스마트하고 지속 가능한 미래를 위한 기술 소개

TI, 임베디드 월드2024에서 스마트하고 지속 가능한 미래를 위한 기술 소개