2배의 성능, 550만 로직 엘리먼트 용량, 이종적 3D SiP 집적, 가장 포괄적인 보안 기능 제공

• Intel 14nm Tri-Gate를 기반으로 하고 혁신적인 HyperFlex 아키텍처를 채택함으로써 Stratix 10 FPGA 및 SoC은 2배의 성능과 지극히 뛰어난 전력 효율을 달성한다.

• 이종 3D SiP(system-in-package) 집적의 새로운 시대를 개막함으로써 차세대 트랜시버 기반 솔루션으로 확장성과 유연성을 가능하게 하고 제품 출시 시간을 단축한다.

• 혁신적인 Secure Device Manager를 도입함으로써 업계에서 가장 포괄적인 고성능 FPGA 보안 기능들을 제공한다.

Altera는 자사의 Stratix® 10 FPGA 및 SoC으로 적용하고 있는 아키텍처 및 기술적 세부사항들을 발표하였다. Stratix 10 제품군은 비약적으로 향상된 성능, 통합 수준, 밀도, 보안성을 제공하는 Altera의 차세대 하이엔드 프로그래머블 로직 디바이스 제품군이다.

Stratix 10 FPGA 및 SoC은 Intel®의 14nm Tri-Gate 프로세스를 기반으로 하고 Altera의 혁신적인 HyperFlex™ FPGA 패브릭 아키텍처를 적용함으로써 이전 세대 FPGA들에 비해서 2배 더 높은 코어 성능을 제공한다. 업계에서 가장 성능이 높고 밀도가 높은 FPGA인데다 첨단의 임베디드 프로세싱, GPU급 부동소수점 연산 성능, 이종적 3D SiP 집적을 결합함으로써 고객들이 이전에 가능하지 않았던 방식으로 차세대 통신, 데이터센터, IoT 인프라, 방위, 고성능 컴퓨팅 시스템의 까다로운 요구를 충족할 수 있도록 한다.

Altera의 마케팅 선임 부사장인 Danny Biran은 “우리 회사가 Stratix 10 FPGA 및 SoC으로 제공하는 성능은 업계에서 지금까지는 전혀 생각할 수 없었던 수준이다. Stratix 10 FPGA 및 SoC을 이용함으로써 고객들은 지금까지는 FPGA로 할 수 없었던 방식으로 시스템을 설계하고 혁신을 이룰 수 있게 되었다”고 말했다.

HyperFlex 아키텍처, 모든 곳으로 레지스터 도입

Stratix 10 FPGA 및 SoC은 Altera 디바이스로서 최초로 Altera의 새로운 HyperFlex 아키텍처를 채택하고 있다. HyperFlex 아키텍처는 지금까지 10년의 기간 동안에 FPGA 업계에서 가장 의미 있는 패브릭 아키텍처 혁신이 될 것으로 기대된다. Intel의 14nm Tri-Gate 프로세스를 채택함으로 인한 프로세스 노드 상의 우위에다 HyperFlex 아키텍처까지 결합함으로써 경쟁사 차세대 하이엔드 FPGA에 비해서 2배의 코어 로직 주파수 향상을 이루게 되었다.

HyperFlex 아키텍처는 모든 코어 인터커넥트 배선 구역으로 레지스터를 도입함으로써, Stratix 10 FPGA 및 SoC으로 레지스터 리타이밍, 파이프라이닝, 기타 설계 최적화 기법들을 비롯한 검증된 성능 향상 설계 기법들을 활용하는 것을 가능하게 한다. 이러한 설계 기법들은 기존의 FPGA 아키텍처로는 도입하기가 현실적으로 여의치 않았다. HyperFlex 아키텍처는 디자이너들이 주요 경로 및 배선 상의 지연시간을 제거하고 자신의 디자인으로 빠르게 타이밍 종결을 달성할 수 있도록 한다. 또한 2배 더 높은 코어 로직 성능을 달성함으로써 경쟁 아키텍처로는 필요로 하는 지극히 폭넓은 데이터 경로와 스큐를 유발시키는 그 밖의 구조물들을 필요로 하지 않음으로써 디바이스 활용도와 전력을 크게 향상시킨다. HyperFlex 아키텍처는 필요한 로직 면적을 줄임으로써 고성능 디자인을 최고 70퍼센트까지 더 낮은 전력으로 작동할 수 있다. 이 아키텍처에 관한 더 자세한 정보는 www.altera.com/hyperflex에서 볼 수 있다.

이종 3D SiP 집적의 시대 개막

Stratix 10 FPGA 및 SoC 제품군의 모든 제품은 이종적 3D SiP 집적 기술을 이용해서 고밀도 모노리딕 FPGA 코어 패브릭과 여타의 첨단 소자들을 효율적이고 경제성 뛰어난 방식으로 통합하며, 그럼으로써 Stratix 10 FPGA 및 SoC의 확장성과 유연성을 높인다. 모노리딕 코어 패브릭은, 높은 밀도를 제공하기 위해서는 다중의 FPGA 다이를 사용해야 하는 경쟁사 이종 디바이스들을 사용할 때와 같은 접속 문제를 피할 수 있으므로 디바이스 활용도와 성능을 극대화한다. Altera의 이종적 SiP 집적은 Intel의 특허보유 EMIB(Embedded Multi-die Interconnect Bridge) 기술을 활용해서 가능하게 되었다. 이 기술은 인터포저 기반 기법에 비해서 더 높은 성능을 달성하고, 복잡성을 줄이고, 비용을 낮추고, 향상된 신호 무결성을 달성한다.

Stratix 10 제품군의 첫 제품들은 EMIB 기술을 사용해서 고속 직렬 트랜시버 및 프로토콜 타일과 모노리딕 코어 로직을 통합한다. 이종적 3D SiP로 고속 프로토콜 및 트랜시버를 통합함으로써 Altera는 변화하는 시장 요구에 따라서 다양한 유형의 Stratix 10 디바이스 제품 버전을 빠르게 제공할 수 있게 되었다. 예를 들어서 이종적 3D SiP 통합을 통해서 Stratix 10 디바이스로 더 높은 트랜시버 속도(56Gbps), 새롭게 등장하는 변조 형식(PAM-4), 새로운 통신 표준(PCIe Gen4, Multi-Port Ethernet), 그 밖에 아날로그 또는 고대역폭 메모리 같은 기능들을 빠르게 지원할 수 있게 되었다.

Stratix 10 제품군의 다양한 밀도의 제품들로 64비트 ARM® 쿼드코어 Cortex®-A53 하드 프로세서 시스템(HPS)을 통합하고 이와 함께 시스템 메모리 관리 유닛, 외부 메모리 컨트롤러, 고속 통신 인터페이스 등의 풍부한 주변장치 기능 셋을 제공한다. Stratix 10 SoC을 앞세워서 Altera는 하이엔드 SoC FPGA를 공급하는 유일한 회사로서 업계에서의 선도적인 위치를 더욱 더 강화하게 되었다. 이 범용성 뛰어난 컴퓨팅 플랫폼은 지극히 뛰어난 적응성, 성능, 전력 효율, 시스템 통합, 설계 생산성을 가능하게 함으로써 다양한 유형의 고성능 애플리케이션에 이용하기에 적합하다. 설계자들은 자사의 고성능 시스템으로 Stratix 10 SoC을 사용함으로써 하드웨어 가상화를 할 수 있을 뿐만 아니라 가속화 프리-프로세싱, 원격 업데이트 및 디버그, 구성, 시스템 성능 모니터링 같은 관리 및 모니터링 기능들을 추가할 수 있을 것이다.

포괄적인 보안 기능들을 통합함으로써 최대의 디자인 보호 달성

Stratix 10 FPGA 및 SoC은 고성능 FPGA로 업계에서 가장 포괄적인 보안 기능들을 통합한다. 이를 위한 핵심적 요소가 혁신적인 Secure Design Manager(SDM)이다. Secure Design Manager는 섹터 기반 인증 및 암호화, 다중 인자 인증, PUF(physically unclonable function) 기술 같은 보안 기능들을 제공한다. Altera는 Athena Group과 IntrinsicID를 비롯한 파트너사들과 협력을 통해서 Stratix 10 FPGA 및 SoC으로 세계 정상의 암호화 가속화 및 PUF IP를 제공한다. 이와 같은 보안 수준을 달성함으로써 Stratix 10 FPGA 및 SoC은 방위, 클라우드 보안, IoT 인프라 등의 애플리케이션에 이용하기에 이상적으로 적합한 솔루션을 제공한다. 이러한 애플리케이션들에서는 다층적인 보안과 분리적인 IP 보호를 중요하게 요구하기 때문이다.

Stratix 10 FPGA 및 SoC에 이용하도록 Enpirion PowerSoC 제공

Stratix 10 FPGA 및 SoC에 이용하도록 Altera의 Enpirion PowerSoC 전원 솔루션을 지원한다. Enpirion PowerSoC은 엄격한 성능 및 전원 상의 요구를 충족할 수 있을 뿐만 아니라 극히 소형화된 풋프린트로 높은 효율을 달성한다.

수백만 LE 디자인으로 빠르게 타이밍 종결 달성

Altera의 Quartus® II 소프트웨어에 도입하고 있는 새로운 Spectra-Q 엔진은 HyperFlex 아키텍처로부터 비롯되는 성능, 전력, 면적 절약의 이점을 극대화하도록 하면서 또한 Stratix 10 FPGA 및 SoC을 이용하는 디자이너의 설계 생산성을 향상시키고 제품 출시 시간을 단축하도록 한다. Quartus II 소프트웨어는 최대 8배의 컴파일 시간 단축, 다양한 방식의 신속하게 추적 가능한 설계 입력, 드롭인 IP 통합, OpenCL 지원, 고수준 설계 플로우 등의 새로운 기능들을 추가함으로써 Altera가 설계 소프트웨어 있어서도 한 걸음 더 앞서나가도록 하고 있다. Spectra-Q 엔진에 관한 더 자세한 정보는 www.altera.com/spectraq에서 볼 수 있다.

Stratix 10 FPGA 및 SoC의 기술적 특징 요약:

• 모노리딕 다이로 최대 550만 로직 엘리먼트 제공

• 이종적 3D SiP 집적을 통해서 FPGA 패브릭과 고속 트랜시버 통합

• 최대 144개 트랜시버를 통합함으로써 이전 세대 제품들에 비해서 4배의 직렬 대역폭 제공

• 최대 1.5GHz로 동작하는 64비트 쿼드코어 ARM Cortex-A53 하드 프로세서 서브시스템 통합

• 하드 부동소수점 DSP를 통합함으로써 최대 10 TFLOPS 쓰루풋에 이르는 단정도 연산 가능

• Secure Device Manager: 포괄적인 고성능 FPGA 보안 기능 제공

• 앞선 SEU(single-event upset) 검출 및 스크러빙

• Arria® 10 FPGA 및 SoC과 풋프린트 호환이 가능하므로 편리하게 이전 가능

• Altera Enpirion 전원 솔루션을 이용함으로써 전력 효율 극대화 및 보드 면적 절약

• Intel의 14nm Tri-Gate 프로세스 기술 적용

공급

디자이너들은 Fast Forward Compile 성능 평가 툴을 이용함으로써 Stratix 10 디자인 개발 작업을 지금 바로 시작할 수 있다. Stratix 10 FPGA 및 SoC의 엔지니어링 샘플을 2015년 가을부터 공급할 예정이다. 임베디드 소프트웨어 개발자들은 Mentor Graphics에서 제공하는 SoC 가상 플랫폼을 활용함으로써 Stratix 10 SoC 임베디드 소프트웨어 개발 작업을 가속화할 수 있다. Stratix 10 FPGA 및 SoC 제품에 관한 더 자세한 내용은 현지의 Altera 영업 사무소로 문의하거나 www.altera.com/stratix10에서 볼 수 있다.

전망적 진술

이 보도자료는 1995년 증권 민사 소송 개혁법(Private Securities Litigation Reform Act)의 면책 조항에 근거해서 Stratix 10 FPGA 및 SoC과 이의 엔지니어링 샘플 공급에 관한 전망적 진술을 포함한다. 투자자들은, 이러한 전망적 진술은 실제 결과가 이러한 현재 예상과 달라질 수 있는 위험성과 불확실성을 포함한다는 점에 유의해야 한다. 이러한 위험성 및 불확실성에 대해서는 Altera의 증권 거래 위원회(Securities and Exchange Commission) 제출 문서에서 논의하고 있다. 이 문서는 Altera 웹사이트에 게재하고 있으며 Altera에 요청하면 무료로 받아볼 수 있다.

관련 링크 : http://www.altera.com/hyperflex

저작권©올포칩 미디어. 무단전재 및 재배포를 금지합니다.

- MOXA, 스마트 그리드용 새로운 첨단 미터링 솔루션 출시AMI(Advanced Metering Infrastructure) 솔루션 선도 업체인 MOXA는 스마트 그리드에 이용하기 위한 산업용 사물인터넷(IoT; Internet of Things) AMI 솔루션을 출시한다고 밝혔다

- 인피니언, 보호 기능을 통합한 지능형 전력 모듈 MIPAQ™ Pro 출시인피니언 테크놀로지스(코리아 대표이사 이승수)는 지능형 전력 모듈(IPM) 신제품인 MIPAQ™ Pro를 출시했다. MIPAQ™ Pro는 풍력발전, 태양광, 산업용 드라이브 등의 애플리케이션에 사용되는 다양한 유형의 컴팩트한 인버터 디자인을 위한 “올인원” 솔루션이다.

- 프리스케일, 구리 배선 조립 기술이 통합된 부품 출하 10억 개 돌파프리스케일 반도체(www.freescale.co.kr 한국 대표이사 황연호)는 업계 전반에 걸쳐 구리 배선 조립 기술의 사용을 확장 및 촉진한다는 야심 찬 전략을 출범한지 불과 2년 만에 10억 개째 구리 배선 부품을 출하했다.

- 리니어, 동시 샘플링 가능한 옥탈ADC 출시리니어 테크놀로지 코리아(대표 홍사곽)는 업계를 선도하는 성능 및 유연성을 갖춘 18비트 8채널 동시 샘플링 SAR(successive approximation register) ADC(제품명: LTC2348-18)를 출시한다고 밝혔다.

- ams, 필수안전 자동차 애플리케이션에 이상적인 고속 로터리 위치 센서 출시고성능 아날로그 IC 및 센서 전문기업인 ams(지사장 이종덕)는 ISO26262 기능안전 국제표준 요건에 부합하여 자동차 애플리케이션에서 뛰어난 신뢰성을 실현하는 초고속 마그네틱 로터리 위치 센서(제품명: AS5147P)를 출시했다고 밝혔다.

- 마이크로칩, 세계 최초 컨피규레이션 가능한 아날로그 출력 및 2-와이어 디지털 버스 내장 하이-사이드 전류/전력 센서 출시마이크로컨트롤러, 혼합 신호, 아날로그 및 플래시-IP 솔루션 분야의 세계적인 리더인 마이크로칩테크놀로지(한국대표: 한병돈)는 센서 엑스포(Sensors Expo)에서 아날로그 및 디지털 전류 센서를 결합한 PAC1921을 출시한다고 밝혔다.

- 실리콘랩스, 최고 유연성의 듀얼모드 방식 블루투스 모듈 솔루션 출시 IoT(Internet of Things)용 무선 접속 솔루션 전문기업인 실리콘랩스(Silicon Labs, 지사장 백운달)는 듀얼모드 방식의 Bluetooth® Smart Ready 모듈 솔루션을 출시했다고 밝혔다

- TI의 새로운 SimpleLink™ SensorTag 개발 키트로 3분 이내에 센서를 클라우드에 접속할 수 있어 TI (대표이사 켄트 전)는 센서 데이터와 무선 클라우드 커넥티비티를 결합한 새로운 개발 키트인 차세대 SimpleLink™ SensorTag를 발표한다고 밝혔다. 이 SensorTag 개발 키트는 사용자가 사물인터넷(IoT) 개발에 빠르게 착수할 수 있도록 다음과 같은 기능들을 제공한다:

- 프리스케일, 셀룰러 기지국의 무선 개발 기준을 재정립할 에어패스트(Airfast) 디지털 프런트 엔드 프로세서 발표프리스케일 반도체(www.freescale.com 대표이사 황연호)는 업계 최초로 완벽하게 소프트웨어 프로그래밍 가능한 셀룰러 기지국 무선용 DFE(Digital Front End) SoC(시스템 온 칩)를 발표했다. 이 디바이스는 사실상 하드웨어 로직 설계가 필요 없으므로 고객들이 소프트웨어 개발과 제품 완성에 좀 더 집중할 수 있다.

- 플리어시스템, 군포지샘병원에 열감지 카메라 무상 제공전세계 열화상 카메라 시장점유율 1위인 열화상 전문기업 플리어시스템 한국지사(FLIR Systems Korea, 한국 대표: 앤드류 칼톤 타이크)는 메르스(MERS, 중동호흡기증후군) 검역 보조장비로 활용하도록 군포지샘병원에 FLIR E60 열감지 카메라를 무상으로 제공한다고 밝혔다.

- NI, 새로운 CompactDAQ 컨트롤러로 측정 시스템 단순화NI는 척박한 환경에서 채널 카운트가 높은 어플리케이션을 지원할 수 있는 CompactDAQ 8슬롯 컨트롤러를 출시했다. 프로세서와 신호 컨디셔닝 및 I/O를 하나의 CompactDAQ 시스템에 통합한 이 제품을 통해 엔지니어들은 측정의 정확도를 향상시키면서도 전반적인 시스템 비용을 절감하고 복잡한 시스템을 단순화할 수 있다.

- 리니어 테크놀로지, 36V, 800mA 견고한 선형 레귤레이터 출시 리니어 테크놀로지 코리아(대표 홍사곽)는 견고한 800mA 폭넓은 입력 전압 범위의 선형 레귤레이터(제품명: LT3088)를 출시한다고 밝혔다.

- TI, 폐루프 전류 감지 기능 제공 업계 최초의 완전 통합형 플럭스게이트 센서, 신호 컨디셔닝 및 보상 코일 드라이버 IC출시TI (대표이사 켄트 전)는 새로운 자기 감지 집적회로(IC)를 출시한다고 밝혔다. 신제품 DRV421은 업계 최초로 필요한 모든 신호 컨디셔닝 회로와 함께 플럭스게이트(Fluxgate) 센서 및 보상 코일 드라이버를 완전히 통합하였다.

- 리니어, 고집적 2.5A 백업 파워 매니저 출시리니어 테크놀로지 코리아(대표 홍사곽)는 주 전원 오류가 발생할 때 활성상태로 유지해야 하는 3.5V ~ 5V 전원 레일에 적합한 통합형 리튬이온 배터리 백업 전력 관리 시스템(제품명: LTC4040)을 출시했다고 밝혔다

TI와 델타 일렉트로닉스, 전기차 온보드 충전 발전을 위한 협력 발표

TI와 델타 일렉트로닉스, 전기차 온보드 충전 발전을 위한 협력 발표 ST, 자체 기술로 AI 지원 제품 개발 가속화하는 ST 엣지 AI 스위트 출시

ST, 자체 기술로 AI 지원 제품 개발 가속화하는 ST 엣지 AI 스위트 출시 마우저, 양자 컴퓨팅의 잠재력을 탐구하는 기술 및 솔루션 저널 ‘메소드(Methods)’ 최신호 공개

마우저, 양자 컴퓨팅의 잠재력을 탐구하는 기술 및 솔루션 저널 ‘메소드(Methods)’ 최신호 공개 한국레노버, 비즈니스 노트북 레노버 V15 4세대 오픈마켓 판매 시작

한국레노버, 비즈니스 노트북 레노버 V15 4세대 오픈마켓 판매 시작 NCH코리아, 분말형 세척제 ‘스필 드래곤’ 출시

NCH코리아, 분말형 세척제 ‘스필 드래곤’ 출시

- 지멘스-소니, Siemens Xcelerator로 설계된 시스템으로 몰입형 엔지니어링 구현

- 키사이트, RFIC 칩 설계자를 위한 차세대 무선 주파수 회로 시뮬레이터 출시

- 베바스토 코리아, ‘글로벌 소셜 위크’ 진행

- 디지키, ‘스마트 세상에서의 AI’를 다룬 시티 디지털 시즌 4 동영상 시리즈 발표

- 지멘스와 인텔 파운드리 협력, 지능형 IC 설계 및 검증을 위한 AI 가속 시뮬레이터 발표

- 인텔, 업계 최초 완전 통합형 광학 I/O 칩렛 구현

그래픽 / 영상

많이 본 뉴스

제13회 '매트랩 엑스포 2024 코리아' 개최 - 최신 기술 트렌드에 대한 인사이트 제공

제13회 '매트랩 엑스포 2024 코리아' 개최 - 최신 기술 트렌드에 대한 인사이트 제공 온세미, 데이터센터의 에너지 효율 향상 위한 완전한 ‘전력 솔루션’ 공개

온세미, 데이터센터의 에너지 효율 향상 위한 완전한 ‘전력 솔루션’ 공개 서비스나우, K24에서 전략적 파트너십 확대 공개

서비스나우, K24에서 전략적 파트너십 확대 공개 마이크로칩, 전기차 충전기 설계를 위한 온보드 충전기 솔루션 출시

마이크로칩, 전기차 충전기 설계를 위한 온보드 충전기 솔루션 출시 엔비디아, 디지털 휴먼 마이크로서비스 출시, 생성형 AI 아바타 미래 열어

엔비디아, 디지털 휴먼 마이크로서비스 출시, 생성형 AI 아바타 미래 열어 마이크로칩, VS Code용 MPLAB 익스텐션 얼리억세스 버전 출시

마이크로칩, VS Code용 MPLAB 익스텐션 얼리억세스 버전 출시 로데슈바르즈와 IPG 오토모티브, 자동차 레이더의 완벽한 HIL 테스트 솔루션 공개

로데슈바르즈와 IPG 오토모티브, 자동차 레이더의 완벽한 HIL 테스트 솔루션 공개 로데슈바르즈의 USB 3.2 Gen 1/2 송수신 적합성 테스트 솔루션, USB-IF 승인 획득

로데슈바르즈의 USB 3.2 Gen 1/2 송수신 적합성 테스트 솔루션, USB-IF 승인 획득 한국레노버, AI 지원 모바일 워크스테이션 신제품 5종 출시

한국레노버, AI 지원 모바일 워크스테이션 신제품 5종 출시 온세미, 최신 7세대 IGBT 모듈로 설계 간소화와 비용 절감 지원

온세미, 최신 7세대 IGBT 모듈로 설계 간소화와 비용 절감 지원

자동차 애플리케이션을 위한 안전한 블루투스 LE 연결

자동차 애플리케이션을 위한 안전한 블루투스 LE 연결 헤드셋 매출의 향방, 하락세는 지속할 것인가?

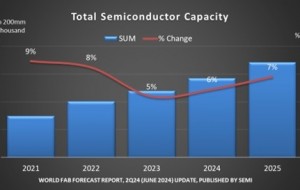

헤드셋 매출의 향방, 하락세는 지속할 것인가? 한국 반도체 생산능력, 올해 첫 5백만장 넘어선다

한국 반도체 생산능력, 올해 첫 5백만장 넘어선다