이번 발표는 파리에서 열린 CMP의 연례 사용자 회의에서 이뤄졌다. CMP 연례 사용자 회의는 CMP의 멀티 프로젝트 웨이퍼 서비스를 사용하거나 관심을 갖고 있는 학계, 연구기관 또는 사기업 대표들을 위한 공개 행사로서, 참가 단체들은 보통 수십에서 수천 개에 달하는 소량의 첨단 IC를 입수할 수 있다.

45nm CMOS 공정기술의 도입은 대학에서 65nm 및 90nm와 같은 이전 CMOS 기술 세대를 이용할 수 있게 한 성공적인 협력을 바탕으로 구축되었다. 일례로, 지금까지 100개 이상의 대학들 (유럽 60%, 북미 및 아시아 40%)이 ST의 65nm 벌크 CMOS 공정기술을 위한 설계 규칙 및 설계 키트를 받았다. 또한 CMP 연례 회의에서 ST와 CMP는 학계를 위한 CMP의 기술 포트폴리오에 ST의 SOI 프로세스 기반 CMOS 65nm를 추가했다고 밝혔다. SOI 기판 상에 설계된 디바이스는 벌크 기판을 이용한 동일한 디자인보다 훨씬 더 높은 성능과 낮은 전력 소비를 나타낸다. 뿐만 아니라 SOI 기술은 방사선에 더 강하여, 우주 애플리케이션 등에 더 적합하다.

CMP의 베르나르 쿠르트와 (Bernard Courtois) 이사에 의하면 최근 몇 년 사이에 생산된 CMOS 디바이스의 수가 급격히 증가했다. 예를 들어 2007년에 90nm CMOS로 설계된 총 회로수는 거의 100% 증가하였다. 2007년에 91개 회로였던 것에 비해서 2006년에는 57개, 2005년에는 32개였다. 또한 대부분의 유수 대학들이 이제 65nm로 디자인을 준비하고 있다.

ST마이크로일렉트로닉스의 프론트엔드 기술 및 제조 부문, 대학 및 외부 협력 담당 이사인 패트릭 코제 (Patrick Cogez)는 “이 흥미로운 프로그램은 ST가 교육 및 연구 커뮤니티와의 강력한 관계를 구축하고 있음을 잘 보여준다. 대학생들과 연구원들은 가장 최신의 기술들을 접하는 것이 필수적다. ST는 20년에 걸쳐서 CMP와 협력해서 이를 제공하고 있다. 또한 ST는 장기적으로 기술 선도 기업으로 남기 위한 노력의 일환으로, 대학들이 ST의 첨단 기술을 접할 수 있도록 보장함으로써 우수한 젊은 엔지니어들에게 좋은 인상을 심어줄 수 있다”고 말했다.

저작권©올포칩 미디어. 무단전재 및 재배포를 금지합니다.

- 마이크로 디바이스 새로운 고속 PicoGuard XS™ ESD 아키텍처 출시캘리포니아 마이크로 디바이스가 새로운 혁신적인 ESD 아키텍처인 PicoGuard XS를 출시했다.

- AMD 옵테론 프로세서 스토리지 분야에서 성장세 지속AMD는 금일 최상의 성능 및 안정성, 뛰어난 에너지 효율성 및 가상화 기술에 힘입어 엔터프라이즈용 스토리지 업체들의 AMD 옵테론 프로세서 채택이 지속적으로 증가하고 있다고 발표했다.

- 업계 최초로 고속 연속 시간 시그마-델타 아날로그-디지털 컨버터 출시고성능 아날로그 신호 경로 제품 분야의 기술을 선도하는 내셔널 세미컨덕터 코리아는 업계 최초로 고속 연속 시간 시그마-델타(1)(이하 CTSD) AD 컨버터(Analog-to-Digital Converter) 를 출시한다고 발표했다.

- 파나소닉 일렉트로닉 디바이스 디지털 카 TV 튜너에 인피니언의 튜너 IC 채택아날로그 및 디지털 튜너 IC 분야의 선도업체인 인피니언 테크놀로지스는 파나소닉 일렉트로닉 디바이스가 자사의 디지털 카 TV 튜너에 인피니언의 OmniTune™ TUA6045 RF 튜너 IC를 채택했다고 발표했다.

- ARM 프로세서 공급 100억 개 돌파ARM은 자사의 파트너 기업들을 통해 선적한 프로세서 수가 100억 개를 넘어섰다고 발표했다. 1991년 첫 RISC 코어인 ARM6™ 프로세서를 선보인 바 있으며, 현재는 반도체 파트너 기업들을 통해 매년 거의 30억 개에 달하는 ARM Powered® 프로세서를 공급하고 있다.

- 프리스케일 매스 마켓 대상의 보급형 ColdFire® 코어 발표프리스케일 반도체는 반도체 기술 라이센싱 전문업체인 IP익스트림을 통해 32비트 V1 ColdFire 코어의 임베디드 커뮤니티 공급으로 ColdFire® 라이센싱 프로그램을 확대해왔다.

- 유블럭스의 GPS 칩 유플레이의 골프 거리 측정기에 채택골프거리 측정기 전문업체인 유플레이가 스위스의 선두 GPS 수신기 기술 제공업체인 유블럭스의 GPS 칩을 자사의 새 제품인 uPro에 채택했다.

- AMD 임베디드 시장 공략 강화를 위한 다양한 솔루션 대거 선보여AMD는 임베디드 시스템 개발자들을 위해 한층 향상된 플랫폼 안정성 및 에너지 효율성, 비주얼 성능을 제공하는 프로세서 및 칩셋, 그래픽 프로세서 솔루션 신제품들을 대거 선보인다고 발표했다.

- TI 신임 회장에 리치 템플턴 임명TI의 토마스 엔지버스 회장이 4월 17일에 열리는 주주 회의를 마지막으로 퇴임한다. 이에 따라 지난 15년간 함께 TI를 이끌어 온 리차드 템플턴 사장 겸 CEO가 신임 회장으로 내정되었다.

- 업계에서 가장 낮은 노이즈를 구현하는 오디오 버퍼 출시고성능 아날로그 신호 경로 제품 분야의 기술을 선도하는 내셔널 세미컨덕터 코리아은 전문가용 오디오 애플리케이션을 위한 업계 최저의 노이즈 및 고조파 왜곡을 구현하는 새로운 버퍼를 출시한다고 발표했다.

- 인터넷 라디오 지원 무선 디지털 액자 플랫폼 설계 위해 텔레칩스와 파트너십 체결영국 캠브리지– CSR plc는 자사의 UniFi 싱글칩 와이파이 기술이 텔레칩스의 와이파이 지원 디지털 사진 액자 플랫폼에 탑재되어 무선 연결 기능을 제공한다고 밝혔다.

- AMD 페넘TM 9600 블랙 에디션 쿼드 코어 프로세서 출시AMD는 고성능 프로세서를 원하는 사용자들을 위해 클럭 배수 조절을 통해 유저가 직접 성능을 튜닝할 수 있도록 클럭 배수를 풀어놓은 AMD 페넘 9600 블랙 에디션 쿼드 코어 프로세서를 새롭게 출시했다.

- 모바일 뮤직 애플리케이션을 위해 24-비트 Hi-Fi 오디오급 DAC 출시모바일 멀티미디어 분야의 세계적 기업인 ST마이크로일렉트로닉스는 전체 오디오 경로에 걸쳐 103dB 동적 범위를 제공하는 고성능 24-bit 오디오 DAC를 출시했다.

- 아날로직테크 듀얼 입력/싱글 출력 파워 서플라이 셀렉터 스위치 개발모바일 컨수머 전자제품용 전력 관리 반도체 개발업체인 아날로직테크는 저 드롭아웃 기능의 새로운 듀얼 입력/싱글 출력 파워 서플라이 셀렉터(selector) 스위치 2종을 개발했다고 밝혔다.

로지텍, 친환경 패션 브랜드 ‘플리츠마마’와 브랜드 콜라보 진행

로지텍, 친환경 패션 브랜드 ‘플리츠마마’와 브랜드 콜라보 진행 마이크로칩, 우주 애플리케이션 위한 내방사선 PolarFire SoC FPGA 출시

마이크로칩, 우주 애플리케이션 위한 내방사선 PolarFire SoC FPGA 출시 마우저, 미래의 엔지니어 및 혁신가 양성을 위해 Ten80 STEM 챌린지 후원

마우저, 미래의 엔지니어 및 혁신가 양성을 위해 Ten80 STEM 챌린지 후원 델 테크놀로지스, 사이버 복원력 강화한 데이터보호 어플라이언스 신제품 출시

델 테크놀로지스, 사이버 복원력 강화한 데이터보호 어플라이언스 신제품 출시 테스트웍스, ETRI의 메타버스 개발 과제를 위한 3D 데이터 셋 구축 사례 공개

테스트웍스, ETRI의 메타버스 개발 과제를 위한 3D 데이터 셋 구축 사례 공개

- 로지텍, 미니멀 라이프를 즐기자: ‘미니멀테리어’에 최적화된 추천 아이템 3

- 마이크로칩, 임베디드 보안 기능을 간단하게 통합할 수 있는 32비트 마이크로컨트롤러 출시

- 한국마이크로소프트, AI 기술의 미래 조명하는 ‘AI Tour in Seoul’ 개최

- 미루웨어, 국제인공지능대전(AI EXPO) 2024 참가

- 플리어의 T5xx 전문가용 열화상 카메라, 전기시설 점검을 위한 필수 장비로 활용

- 델 테크놀로지스 보고서, 생성형 AI가 기업의 성과 창출에 기여

그래픽 / 영상

지멘스 EDA, 최첨단 SoC 설계를 위한 혁신적인 에뮬레이션 및 프로토타이핑 솔루션 발표

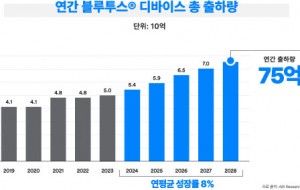

지멘스 EDA, 최첨단 SoC 설계를 위한 혁신적인 에뮬레이션 및 프로토타이핑 솔루션 발표 블루투스 지원 기기 출하량, 향후 5년 동안 연평균 8% 성장 전망

블루투스 지원 기기 출하량, 향후 5년 동안 연평균 8% 성장 전망 인터넷의 ‘필터 버블(Filter Bubble)’ 깨부수기

인터넷의 ‘필터 버블(Filter Bubble)’ 깨부수기

많이 본 뉴스

델 테크놀로지스, 2024년 AI 시대를 위한 광범위한 클라이언트 신제품 공개

델 테크놀로지스, 2024년 AI 시대를 위한 광범위한 클라이언트 신제품 공개 마이크로칩, 항공기 전기화 전화를 간소화하는 통합 구동 파워 솔루션 출시

마이크로칩, 항공기 전기화 전화를 간소화하는 통합 구동 파워 솔루션 출시 써모 피셔, 인터배터리 2024에서 분석 토탈 솔루션 선보여

써모 피셔, 인터배터리 2024에서 분석 토탈 솔루션 선보여 인텔 가우디 2, 최신 MLPerf 벤치마크를 통해 생성형 AI의 지속적인 성능 향상 입증

인텔 가우디 2, 최신 MLPerf 벤치마크를 통해 생성형 AI의 지속적인 성능 향상 입증 콩가텍, ctrlX OS 지원으로 컴퓨터 온 모듈 포트폴리오 강화

콩가텍, ctrlX OS 지원으로 컴퓨터 온 모듈 포트폴리오 강화 ST, 2세대 MPU로 지능형 엣지 애플리케이션의 성능 향상 및 산업 탄력성 지원

ST, 2세대 MPU로 지능형 엣지 애플리케이션의 성능 향상 및 산업 탄력성 지원 글로벌 300mm 팹 장비 투자액, 2025년 20% 증가

글로벌 300mm 팹 장비 투자액, 2025년 20% 증가 2023년 글로벌 반도체 장비 지출액 전년대비 1.3% 감소

2023년 글로벌 반도체 장비 지출액 전년대비 1.3% 감소 쿤텍-시큐어아이씨, 임베디드 분야 보안 강화 지원하는 파트너십 체결

쿤텍-시큐어아이씨, 임베디드 분야 보안 강화 지원하는 파트너십 체결 인텔, AI PC 소프트웨어 개발자 및 하드웨어 벤더를 위한 신규 프로그램 발표

인텔, AI PC 소프트웨어 개발자 및 하드웨어 벤더를 위한 신규 프로그램 발표