프로그래머블 솔루션 분야에서 차별화된 저전력 리더십으로 시장을 선도하고 있는 래티스 반도체(Lattice Semiconductor)가 로직 셀 용량과 메모리, SERDES 등 내부 아키텍처 성능을 대폭 향상시킨 미드레인지급 FPGA 플랫폼을 출시하고, 시장 확대에 나서고 있다.

래티스의 아방트(Avant)는 통신, 컴퓨팅, 산업 및 자동차 시장의 보다 다양한 애플리케이션 요구사항에 대응할 수 있도록 동급 최상의 전력 효율성과 첨단 연결 기능 및 최적화된 컴퓨팅 성능에 중점을 두고 개발되었다. 또한 래티스는 아방트 플랫폼을 기반으로 향후 다양한 제품군을 구축하여 포트폴리오를 확장할 예정이다.

래티스 반도체 코리아의 윤장섭 사장은 “설계의 효율성 및 유연성에 대한 요구와 연결성 및 인텔리전스에 대한 수요가 빠르게 증가하면서 이에 대응할 수 있는 미드레인지급 FPGA를 출시하게 되었으며, 이를 통해 유효 시장 규모가 2배로 증가했다. 래티스는 저전력 리더십을 기반으로 지속적으로 FPGA의 성능과 용량을 확장함으로써 타깃 시장을 확장해 나갈 것이다.”고 밝혔다.

아방트 FPGA 플랫폼은 저전력 구현을 위한 프로그래머블 패브릭과 설정이 가능한 25G SERDES 및 8개의 PCIe 전용 4세대 컨트롤러를 내장하고 있다. 또한 DDR5까지 지원 가능한 고속 메모리 인터페이스를 지원하고, AI 추론을 처리할 수 있는 향상된 DSP를 비롯해 첨단 암호화 알고리즘을 갖추고 있다. 아방트는 이전 세대인 넥서스(Nexus) 플랫폼 대비 5배 더 높은 로직 셀 용량과 10배 더 높은 대역폭, 30배 더 빠른 성능을 제공한다.

래티스코리아의 윤장섭 지사장(왼쪽)과 이기훈 부장

래티스 반도체 코리아의 이기훈 부장은 “TSMC 16nm FinFET 공정 기술과 최적화된 내부 아키텍처로 구현된 아방트 FPGA는 경쟁사의 동급 제품 대비 최대 2.5배 낮은 전력소모와 2배 더 빠른 시리얼 대역폭 성능을 제공한다.”며, “또한 아방트는 설계 툴과 레퍼런스 디자인 및 SDK, IP 포트폴리오 등의 기존의 소프트웨어 솔루션 스택을 모두 활용할 수 있어 고객들이 보다 효율적으로 개발을 수행하고, 시장 출시시간을 단축할 수 있다.”고 밝혔다.

래티스의 아방트 플랫폼은 현재 출시된 아방트-E FPGA 제품군을 시작으로 다양한 신규 디바이스 제품군의 신속한 개발이 가능한 확장성 있는 설계 구조를 갖추고 있다. 래티스 아방트-E FPGA는 동급 최고의 전력 효율과 크기 및 성능은 물론, 데이터 프로세싱 및 AI와 같은 엣지 애플리케이션의 요구 사항에 최적화된 기능 세트와 함께 엣지의 주요 과제를 해결할 수 있도록 설계되었다.

진선옥 기자 (jadejin@all4chip.com)

저작권©올포칩 미디어. 무단전재 및 재배포를 금지합니다.

다쏘시스템, 블루 스피릿 에어로와 수소 동력 항공기 개발 가속화블루 스피릿 에어로는 불과 몇 달 만에 3D익스피리언스 플랫폼을 기반으로 하는 “리인벤트 더 스카이” 산업 솔루션을 활용하여 드래곤플라이 형태의 상세한 3D설계를 완성하고 공기 역삭, 구조 에너지 성능을 테스트 및 검증했다. 처음부터 클라우드기반의 가상 환경을 통해 블루 스피릿 에어로는 내부 프로세스를 구조화하고 다양한 분야와 지역에 걸쳐 전분간의 커뮤니케이션을 간소화하여 보다 효율적인 의사결정과 검증을 할 수 있었다.

다쏘시스템, 블루 스피릿 에어로와 수소 동력 항공기 개발 가속화블루 스피릿 에어로는 불과 몇 달 만에 3D익스피리언스 플랫폼을 기반으로 하는 “리인벤트 더 스카이” 산업 솔루션을 활용하여 드래곤플라이 형태의 상세한 3D설계를 완성하고 공기 역삭, 구조 에너지 성능을 테스트 및 검증했다. 처음부터 클라우드기반의 가상 환경을 통해 블루 스피릿 에어로는 내부 프로세스를 구조화하고 다양한 분야와 지역에 걸쳐 전분간의 커뮤니케이션을 간소화하여 보다 효율적인 의사결정과 검증을 할 수 있었다. 엔비디아, 기업 성공 가속화하는 엔비디아 AI 엔터프라이즈 3.0 발표엔비디아 AI 엔터프라이즈 3.0은 컨택 센터 지능형 가상 비서, 음성 전사(transcription), 사이버보안 디지털 지문 채취를 위한 솔루션 워크플로를 도입한다. 이들은 보다 나은 고객 서비스를 제공하고자 흔히 사용되는 AI 채택 기업용 애플리케이션이다. 또한 엔비디아 NGC 소프트웨어 카탈로그에서 제공되는 50가지 이상의 엔비디아 AI 소프트웨어 프레임워크 및 사전 훈련된 모델에 대한 지원을 확장한다.

엔비디아, 기업 성공 가속화하는 엔비디아 AI 엔터프라이즈 3.0 발표엔비디아 AI 엔터프라이즈 3.0은 컨택 센터 지능형 가상 비서, 음성 전사(transcription), 사이버보안 디지털 지문 채취를 위한 솔루션 워크플로를 도입한다. 이들은 보다 나은 고객 서비스를 제공하고자 흔히 사용되는 AI 채택 기업용 애플리케이션이다. 또한 엔비디아 NGC 소프트웨어 카탈로그에서 제공되는 50가지 이상의 엔비디아 AI 소프트웨어 프레임워크 및 사전 훈련된 모델에 대한 지원을 확장한다. ST, 전기자동차의 성능 및 주행거리 향상시키는 새로운 실리콘 카바이드 전력 모듈 출시ST의 새로운 SiC 전력 모듈은 기아 EV6을 비롯해 여러 차량 모델에서 사용되는 현대자동차의 E-GMP 전기차 플랫폼에 채택됐다. 5종의 새로운 SiC-MOSFET 기반 전력 모듈을 통해 차량 제조업체들은 전기자동차의 트랙션 애플리케이션에 일반적으로 사용되는 동작 전압을 지원하고, 다양한 정격 전력을 유연하게 선택할 수 있다.

ST, 전기자동차의 성능 및 주행거리 향상시키는 새로운 실리콘 카바이드 전력 모듈 출시ST의 새로운 SiC 전력 모듈은 기아 EV6을 비롯해 여러 차량 모델에서 사용되는 현대자동차의 E-GMP 전기차 플랫폼에 채택됐다. 5종의 새로운 SiC-MOSFET 기반 전력 모듈을 통해 차량 제조업체들은 전기자동차의 트랙션 애플리케이션에 일반적으로 사용되는 동작 전압을 지원하고, 다양한 정격 전력을 유연하게 선택할 수 있다. 엔비디아, 도이치은행과 협력해 금융 서비스에 AI 채택 가속화도이치은행은 협력을 통해 AI와 머신 러닝을 위한 센터의 우수한 역량을 더욱 가속화할 예정이다. 도이치은행의 추후 이니셔티브에 따르면 이들은 전 세계 고객에 대한 서비스 제공, 새로운 데이터 기반 상품 및 서비스 개발, 효율성 제고, 기술 인재 채용을 위한 노력에 박차를 가할 것으로 전망된다.

엔비디아, 도이치은행과 협력해 금융 서비스에 AI 채택 가속화도이치은행은 협력을 통해 AI와 머신 러닝을 위한 센터의 우수한 역량을 더욱 가속화할 예정이다. 도이치은행의 추후 이니셔티브에 따르면 이들은 전 세계 고객에 대한 서비스 제공, 새로운 데이터 기반 상품 및 서비스 개발, 효율성 제고, 기술 인재 채용을 위한 노력에 박차를 가할 것으로 전망된다. 인섹시큐리티, 가상화폐 분석 추적 실무 교육 과정 개설이 교육은 ‘안체인에이아이’의 블록체인 및 암호화폐 분석 솔루션을 활용 실제 범죄에 악용된 가상화폐 주소들을 사용하여 실습 위주로 진행된다. AI 기술을 적용하여 암호화폐 거래를 모니터링하고 의심스러운 활동을 감지하며 알려진 취약점에 대해 스마트 계약 코드를 스캔할 수 있는 차세대 블록체인 분석 및 추적 솔루션을 공급하고 있다.

인섹시큐리티, 가상화폐 분석 추적 실무 교육 과정 개설이 교육은 ‘안체인에이아이’의 블록체인 및 암호화폐 분석 솔루션을 활용 실제 범죄에 악용된 가상화폐 주소들을 사용하여 실습 위주로 진행된다. AI 기술을 적용하여 암호화폐 거래를 모니터링하고 의심스러운 활동을 감지하며 알려진 취약점에 대해 스마트 계약 코드를 스캔할 수 있는 차세대 블록체인 분석 및 추적 솔루션을 공급하고 있다. 인텔 랩, 페렐만 의대와 공동 수행한 최대 규모 연합 학습 연구 성과 공개인텔 랩 및 펜실베니아 대학교 페렐만 의과대학은 국제 의료 및 연구 기관이 악성 뇌종양을 식별하도록 돕는 분산 머신러닝 인공지능 방식의 연합 학습을 활용한 공동 연구를 완료했다고 밝혔다. 이 연구는 6개 대륙에 걸쳐 71개 기관에서 조사한 광범위한 데이터 세트를 통해 진행하는 등 가장 대규모의 의료 분야 연합 학습 부문 연구로, 뇌종양 탐지를 33% 개선할 수 있는 능력을 입증했다.

인텔 랩, 페렐만 의대와 공동 수행한 최대 규모 연합 학습 연구 성과 공개인텔 랩 및 펜실베니아 대학교 페렐만 의과대학은 국제 의료 및 연구 기관이 악성 뇌종양을 식별하도록 돕는 분산 머신러닝 인공지능 방식의 연합 학습을 활용한 공동 연구를 완료했다고 밝혔다. 이 연구는 6개 대륙에 걸쳐 71개 기관에서 조사한 광범위한 데이터 세트를 통해 진행하는 등 가장 대규모의 의료 분야 연합 학습 부문 연구로, 뇌종양 탐지를 33% 개선할 수 있는 능력을 입증했다. 한국레노버, 구글과 손잡고 미래형 스마트 교육 비전 제시한국레노버는 학생∙교사∙학교의 디지털 교육 역량 강화를 위한 프로젝트를 구글과 함께 서울, 부산, 대전 등 전국 학교에서 진행했다. 레노버와 구글은 레노버 크롬북 등 스마트 기기를 통해 구글 워크스페이스 포 에듀케이션의 다양한 리소스를 활용, 학생과 교사에게 기술 기반의 평등한 학습 기회를 제공하고창의적 교육 및 디지털 기반 학습 환경 향상을 지원했다.

한국레노버, 구글과 손잡고 미래형 스마트 교육 비전 제시한국레노버는 학생∙교사∙학교의 디지털 교육 역량 강화를 위한 프로젝트를 구글과 함께 서울, 부산, 대전 등 전국 학교에서 진행했다. 레노버와 구글은 레노버 크롬북 등 스마트 기기를 통해 구글 워크스페이스 포 에듀케이션의 다양한 리소스를 활용, 학생과 교사에게 기술 기반의 평등한 학습 기회를 제공하고창의적 교육 및 디지털 기반 학습 환경 향상을 지원했다. 마이크로소프트, 2025년까지 전세계 1000만명에 신규 디지털 스킬 교육 무료 지원전 세계 8,000만 구직자들의 디지털 스킬 리소스에 대한 접근을 돕기 위해 다양한 활동을 하는 마이크로소프트의 글로벌 스킬 이니셔티브 일환이다. 앞으로 5만명에게 링크드인 러닝 장학금을 제공하고, 마이크로소프트는 2025년까지 1,000만명을 목표로 수요가 높은 직종에 대한 디지털 스킬을 교육하고 디지털 인재를 양성한다.

마이크로소프트, 2025년까지 전세계 1000만명에 신규 디지털 스킬 교육 무료 지원전 세계 8,000만 구직자들의 디지털 스킬 리소스에 대한 접근을 돕기 위해 다양한 활동을 하는 마이크로소프트의 글로벌 스킬 이니셔티브 일환이다. 앞으로 5만명에게 링크드인 러닝 장학금을 제공하고, 마이크로소프트는 2025년까지 1,000만명을 목표로 수요가 높은 직종에 대한 디지털 스킬을 교육하고 디지털 인재를 양성한다. KT, ‘글로텔 2022’에서 글로벌 최고 통신사로 선정KT는 글로텔 어워즈 2022에서 최고 통신사, ‘유선 네트워크 진화’, ‘올해의 보안솔루션’ 총 3개 부문의 수상 후보에 올랐다. 최고 통신사 부문은 5G 서비스 등 뛰어난 사업 성과와 기록을 종합적으로 평가해 가장 높은 점수를 받은 통신사에 수여되는 상이다. 글로텔어워즈는 글로벌 ICT 리서치 기관 ‘인포마(INFORMA)’가 전 세계의 우수 통신 기업을 대상으로 진행되는 시상식이다.

KT, ‘글로텔 2022’에서 글로벌 최고 통신사로 선정KT는 글로텔 어워즈 2022에서 최고 통신사, ‘유선 네트워크 진화’, ‘올해의 보안솔루션’ 총 3개 부문의 수상 후보에 올랐다. 최고 통신사 부문은 5G 서비스 등 뛰어난 사업 성과와 기록을 종합적으로 평가해 가장 높은 점수를 받은 통신사에 수여되는 상이다. 글로텔어워즈는 글로벌 ICT 리서치 기관 ‘인포마(INFORMA)’가 전 세계의 우수 통신 기업을 대상으로 진행되는 시상식이다. 엔비디아, 시그래프 아시아 2022에서 ‘옴니버스 DLI 트레이닝 랩’ 진행시그래프 아시아는 전 세계 컴퓨터 그래픽 연구자, 개발자, 예술가들이 참여해 아시아의 컴퓨터 그래픽 분야의 광범위한 최신 주제를 다루는 연례 행사로, 아시아 지역에서 순회 개최된다. 대구에서 열리는 이번 행사에서는 8,000명 이상의 기술 전문가와 700명 이상의 발표자가 참석하며 논문 발표, 전시, 튜토리얼, 게임 등 다양한 프로그램이 진행될 예정이다.

엔비디아, 시그래프 아시아 2022에서 ‘옴니버스 DLI 트레이닝 랩’ 진행시그래프 아시아는 전 세계 컴퓨터 그래픽 연구자, 개발자, 예술가들이 참여해 아시아의 컴퓨터 그래픽 분야의 광범위한 최신 주제를 다루는 연례 행사로, 아시아 지역에서 순회 개최된다. 대구에서 열리는 이번 행사에서는 8,000명 이상의 기술 전문가와 700명 이상의 발표자가 참석하며 논문 발표, 전시, 튜토리얼, 게임 등 다양한 프로그램이 진행될 예정이다. 코닝, 고릴라 글래스 빅터스 2로 내구성에 대한 새로운 기준 수립코닝은 고릴라 글래스 포트폴리오를 확대하며 유리의 한계를 지속적으로 넓히고 있다. 고릴라 글래스 빅터스 2는 새로운 유리 조성으로 이전 세대인 고릴라 글래스 빅터스의 스크래치 내구성을 유지하는 동시에 세계에서 가장 많이 사용되는 가공 소재인 콘크리트와 같은 거친 표면에서 향상된 낙하 성능을 선보인다.

코닝, 고릴라 글래스 빅터스 2로 내구성에 대한 새로운 기준 수립코닝은 고릴라 글래스 포트폴리오를 확대하며 유리의 한계를 지속적으로 넓히고 있다. 고릴라 글래스 빅터스 2는 새로운 유리 조성으로 이전 세대인 고릴라 글래스 빅터스의 스크래치 내구성을 유지하는 동시에 세계에서 가장 많이 사용되는 가공 소재인 콘크리트와 같은 거친 표면에서 향상된 낙하 성능을 선보인다. 텔레다인 플리어, 소형의 방폭 열화상 카메라 출시ATEX 기준을 충족하는 케이스 덕분에, FLIR Cx5 사용자는 폭발 가능성이 있는 위험한 작업 환경에서도 전기 또는 기계 설비를 안전하게 모니터링할 수 있다. 석유 및 가스 공장 또는 화학 공장과 같이 폭발 가능성이 있는 환경에서는 모든 발화원을 철저히 관리해야 한다. 이에, 이러한 잠재 위험 환경에서 사용되는 전자 기기나 장치는 ATEX 제품 규정 또는 그와 유사한 규정(UKEX, IECEx 등)을 준수해야 한다.

텔레다인 플리어, 소형의 방폭 열화상 카메라 출시ATEX 기준을 충족하는 케이스 덕분에, FLIR Cx5 사용자는 폭발 가능성이 있는 위험한 작업 환경에서도 전기 또는 기계 설비를 안전하게 모니터링할 수 있다. 석유 및 가스 공장 또는 화학 공장과 같이 폭발 가능성이 있는 환경에서는 모든 발화원을 철저히 관리해야 한다. 이에, 이러한 잠재 위험 환경에서 사용되는 전자 기기나 장치는 ATEX 제품 규정 또는 그와 유사한 규정(UKEX, IECEx 등)을 준수해야 한다. 하이크비전, AIoT 4대 인텔리전스 사업 전략 및 임베디드 오픈 플랫폼 2.0 버전 공개하이크비전의 ‘쉐이핑 인텔리전스 서밋 2022’은 하이크비전 및 기술 파트너, 학계 및 업계 리더 등이 한 자리에 모여 보안 산업의 미래를 살펴보고, 성공 경로를 모색하고 다양한 인사이트를 공유하는 연례 글로벌 행사로서 지난 2017년부터 개최되어 왔다. 이번 행사에서 하이크비전은 AIoT를 메가트렌드로 선정하여 최신 AIoT 애플리케이션을 경험하고, 성공적인 AIoT 적용 사례를 공유했다.

하이크비전, AIoT 4대 인텔리전스 사업 전략 및 임베디드 오픈 플랫폼 2.0 버전 공개하이크비전의 ‘쉐이핑 인텔리전스 서밋 2022’은 하이크비전 및 기술 파트너, 학계 및 업계 리더 등이 한 자리에 모여 보안 산업의 미래를 살펴보고, 성공 경로를 모색하고 다양한 인사이트를 공유하는 연례 글로벌 행사로서 지난 2017년부터 개최되어 왔다. 이번 행사에서 하이크비전은 AIoT를 메가트렌드로 선정하여 최신 AIoT 애플리케이션을 경험하고, 성공적인 AIoT 적용 사례를 공유했다. TI, 우주 등급 제품 포트폴리오에 내성 강화 및 내방사선 플라스틱 패키지 추가TI는 내성 강화 제품용 SHP(space high-grade in plastic) 제품 검사 규격을 개발하고, 이 SHP 규격을 충족하는 새로운 아날로그-디지털 컨버터(ADC)를 출시했다. 또한, 내방사선 스페이스 EP(Space Enhanced Plastic) 포트폴리오에 새로운 제품군을 추가했다. 플라스틱 패키지는 기존의 세라믹 패키지 대비 설계 시 시스템 차원에서 풋프린트 축소 및 무게와 전력 감소, 출시 비용 절감을 달성할 수 있다.

TI, 우주 등급 제품 포트폴리오에 내성 강화 및 내방사선 플라스틱 패키지 추가TI는 내성 강화 제품용 SHP(space high-grade in plastic) 제품 검사 규격을 개발하고, 이 SHP 규격을 충족하는 새로운 아날로그-디지털 컨버터(ADC)를 출시했다. 또한, 내방사선 스페이스 EP(Space Enhanced Plastic) 포트폴리오에 새로운 제품군을 추가했다. 플라스틱 패키지는 기존의 세라믹 패키지 대비 설계 시 시스템 차원에서 풋프린트 축소 및 무게와 전력 감소, 출시 비용 절감을 달성할 수 있다.

마이크로칩, 보안 기능을 확장한 maXTouch 터치스크린 컨트롤러 제품군 출시

마이크로칩, 보안 기능을 확장한 maXTouch 터치스크린 컨트롤러 제품군 출시 마우저, 2024년 1분기에 1만 종 이상의 신제품 추가

마우저, 2024년 1분기에 1만 종 이상의 신제품 추가 ST, 집약적 움직임 분석 지원하는 관성 모듈로 엣지-AI 센서 제품군 확장

ST, 집약적 움직임 분석 지원하는 관성 모듈로 엣지-AI 센서 제품군 확장 HMS 네트웍스, AGV를 위한 첨단 무선 기술 지원

HMS 네트웍스, AGV를 위한 첨단 무선 기술 지원 리미니스트리트 ‘2024 리미니스트리트 써밋’, 엔터프라이즈 소프트웨어 유지보수 혁신 지원

리미니스트리트 ‘2024 리미니스트리트 써밋’, 엔터프라이즈 소프트웨어 유지보수 혁신 지원

- ST, 2024 지속가능성 보고서 발표

- 마우저, IoT 및 에너지 하베스팅 설계 세미나 개최

- 매스웍스코리아, 다양한 분야의 AI 인재 발굴 위한 ‘제4회 매트랩 대학생 AI 경진대회’ 개최

- 다쏘시스템과 HD현대중공업, 버추얼 트윈 기반 설계-생산 일관화 통합 플랫폼 구축

- ams OSRAM과 도미넌트 옵토 테크놀로지스, 지능형 RGB LED로 스마트 자동차 실내 조명 구현

- 원프레딕트, 산업 AI 설비관리 솔루션으로 국제전기전력전시회 참가

그래픽 / 영상

지멘스 EDA, 최첨단 SoC 설계를 위한 혁신적인 에뮬레이션 및 프로토타이핑 솔루션 발표

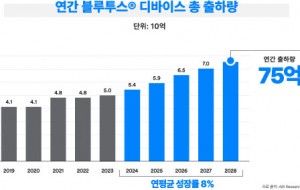

지멘스 EDA, 최첨단 SoC 설계를 위한 혁신적인 에뮬레이션 및 프로토타이핑 솔루션 발표 블루투스 지원 기기 출하량, 향후 5년 동안 연평균 8% 성장 전망

블루투스 지원 기기 출하량, 향후 5년 동안 연평균 8% 성장 전망 인터넷의 ‘필터 버블(Filter Bubble)’ 깨부수기

인터넷의 ‘필터 버블(Filter Bubble)’ 깨부수기

많이 본 뉴스

자이스 코리아, 제약바이오 연구 혁신을 지원하는 최신 고품질 이미징 기술 공개

자이스 코리아, 제약바이오 연구 혁신을 지원하는 최신 고품질 이미징 기술 공개 인텔, AI PC 소프트웨어 개발자 및 하드웨어 벤더를 위한 신규 프로그램 발표

인텔, AI PC 소프트웨어 개발자 및 하드웨어 벤더를 위한 신규 프로그램 발표 인텔 파운드리, 고개구율 극자외선(High-NA EUV) 도입으로 칩 제조 분야 선도

인텔 파운드리, 고개구율 극자외선(High-NA EUV) 도입으로 칩 제조 분야 선도 유블럭스, 위치 정확도를 향상시키는 새로운 GNSS 플랫폼 출시

유블럭스, 위치 정확도를 향상시키는 새로운 GNSS 플랫폼 출시 힐셔, 중앙 관리형 서비스를 제공하는 Edge-IO-Link-Master 출시

힐셔, 중앙 관리형 서비스를 제공하는 Edge-IO-Link-Master 출시 KT, MWC에서 차세대 네트워크 기술과 초거대 AI 공개

KT, MWC에서 차세대 네트워크 기술과 초거대 AI 공개 KT, 노바테크와 손잡고 물류로봇 플랫폼 사업 추진

KT, 노바테크와 손잡고 물류로봇 플랫폼 사업 추진 노르딕 세미컨덕터, CSA의 IoT 기기 보안 사양 1.0 및 인증 프로그램 지원

노르딕 세미컨덕터, CSA의 IoT 기기 보안 사양 1.0 및 인증 프로그램 지원 인섹시큐리티, 다수 모바일 기기 데이터 동시 추출 솔루션 ‘마그넷 그레이키 패스트트랙' 출시

인섹시큐리티, 다수 모바일 기기 데이터 동시 추출 솔루션 ‘마그넷 그레이키 패스트트랙' 출시 취리히 인스트루먼트, 고성능 큐비트 제어를 위한 SHF+ 제품 라인 출시

취리히 인스트루먼트, 고성능 큐비트 제어를 위한 SHF+ 제품 라인 출시