올바른 신호 경로 IC를 선택하면 화상과 음성 모두 최고의 성능을 갖는 제품을 제작할 수 있다. 이러한 신호 경로 IC 각각에는 잡음이나 리플이 없는 “깨끗한” 전력이 필요하게 되고, 전력 관리는 종종 시스템 설계의 마지막 단계로 구현된다. 그림 1은 신호 경로에 전력이 공급되는 방식을 보여주는 시스템 예이다.

그림 1. 신호 경로 IC 성능에 영향을 미치는 전력 공급장치 설계(▶별첨 그림1)

신호 경로 IC 성능에 영향을 미치는 전력 공급장치 설계

전력 공급장치가 아날로그 신호 무결성에 영향을 주고, 궁극적으로 전반적인 시스템 성능에 영향을 미친다는 사실은 너무나도 당연한 것이다. 신호 경로 성능을 개선하는 한 가지 간단한 방법은 올바른 전력 공급장치를 선택하는 것이다. 전력 공급장치를 선택할 때 아날로그 신호 경로 성능에 영향을 미치는 주요 요인은 전력 공급장치 라인에서의 잡음 또는 리플이다. 전력 공급장치의 잡음 또는 리플은 Op 앰프의 출력에 결합되어 PLL(Phase-Locked Loop) 또는 VCO(Voltage-Controlled Oscillator)에서 지터를 증가시키거나 ADC에서 SNR을 떨어뜨린다. 전력 공급장치에서 잡음과 리플이 작으면 신호 경로 성능도 향상된다.

전력 공급장치 라인에서 잡음과 리플이 발생하는 원인은 매우 다양하다. 시스템 자체의 고속 데이터 및 고주파수 신호가 잡음을 일으키는데, 그 이유는 인쇄 회로 기판(PCB) 트레이스 및 와이어링 요소가 잘못 부착될 경우 안테나처럼 동작할 수 있기 때문이다. 마이크로컨트롤러, FPGA(Field Programmable Gate Array), CPLD(Complex Programmable Logic Device) 등과 같은 디지털 IC는 공급되는 전류량이 상황에 따라 다르며, 시스템에 전자기 장애(EMI)를 일으키는 빠른 edge rate를 특징으로 한다. 실리콘 IC는 절대 0도(켈빈 온도) 이상의 온도에서 분자가 무작위로 이동하면서 충돌하기 때문에 내부 열 잡음이 발생한다.

신호 경로에서 잡음과 리플을 최소화하는 방법으로는 신중한 시스템 PCB 레이아웃 설계, 적절한 공급 바이패싱, 올바른 전력 공급장치 선택 등 세 가지가 있다. 시스템에 따라 달라지는 PCB 레이아웃에서는 올바른 구성 요소 배치, 신호 경로 트레이스 길이 최소화, 확실한 접지 확보 등을 고려해야 한다.

공급 레일 바이패싱은 잡음을 걸러내기 위해 대부분의 아날로그 IC 데이터시트에서 권장하는 방법이다. 신호 경로 IC는 별도의 아날로그, 디지털 및 PLL 전력 공급장치 입력을 가질 수 있으며, 각각 권장되는 바이패싱이 다르다. PLL 공급 및 아날로그 공급은 잡음과 리플에 매우 민감하므로, 바이패스 커패시터, 레지스터-커패시터(RC) 필터 및 EMI 억제 필터는 신호 경로 전력 공급장치로 유입되는 잡음과 리플을 최소화 해준다.

올바른 전력 공급장치를 사용하면 신호 경로 IC에 대한 잡음과 리플을 줄일 수 있다. 전력 공급장치를 선택할 때 설계자는 우선 스위칭 컨버터와 리니어 레귤레이터 중에서 선택하게 된다. 스위칭 컨버터는 전체 시스템에서의 전력 소비를 줄이도록 높은 효율성을 제공하며, 리니어 레귤레이터는 공급 레일에서의 잡음/리플을 줄여주는 사용하기 쉬운 솔루션을 제공한다. 리니어 레귤레이터를 사용하면 잡음과 리플을 줄여 신호 경로 성능을 개선할 수 있다.

PSRR(전력 공급 제거비)

아날로그 신호 경로 IC는 부품이 전력 공급장치 라인에서 잡음과 리플을 제거하는 방법을 정의한다. 이 매개변수를 PSRR(전력 공급 제거비)이라고 하며(그림 2 참조), 이는 디바이스로 들어가는 잡음/리플 대 디바이스에서 나오는 잡음/리플의 비율을 나타낸다. PSRR은 데시벨(dB) 단위로 측정되며 해당 방정식은 다음과 같다.

그림 2. 입력에서 출력으로 전환될 때 리플/잡음이 감소하는 크기를 나타내는 PSRR(전력 공급 제거비)(▶별첨 그림2_1, 2_2)

여기에서, V1은 입력 전압 변화이고 V2는 출력 전압 변화를 나타낸다. 이 방정식의 결과 값은 음수이다. 공급자가 PSRR을 양수로 지정해도 문제는 없지만, 이 경우는 V1/V2가 아닌 V2/V1을 사용한 것이기 때문이다. 혼동을 피하기 위해 PSRR의 절대값만을 확인해야하며, 설계자는 출력에서의 잡음/리플을 줄이기 위해 최대한 큰 절대값 PSRR을 원하게 된다. 예를 들어 80 dB(출력 리플이 입력 리플보다 10,000배 더 작음)이 20 dB(출력 리플이 입력 리플보다 10배 더 작음)보다 좋은 것이다.

그림 3은 LMP7711 고정밀 Op 앰프에 대한 PSRR 그래프이다. LMP7711은 1 kHz에서 PSRR이 90 dB인 고정밀 Op 앰프이다. 양의 레일과 음의 레일 모두에 대해 PSRR이 존재하고 리플 주파수 증가에 따라 PSRR도 감소(절대값 감소)한다는 점을 명심해야 한다. 리니어 레귤레이터를 사용하여 신호 경로에 전력을 공급하면 잡음/리플이 감소하는데, 그 이유는 리니어 레귤레이터 역시 입력에서 출력으로 잡음/리플을 제거하기 때문이다. LP5900은 저잡음 100 mA LDO로, 1 kHz에서 PSRR이 85 dB이며, LP5900(저잡음 LDO)을 사용하여 LMP2011(고정밀 Op 앰프)에 전력을 공급하면 전력 공급장치에 대한 잡음/리플이 감소하게 된다(그림 4 참조). 1 kHz 리플/잡음은 85 dB에서 LDO에 의해 제거된 다음 90 dB에서 고정밀 Op 앰프에 의해 제거된다.

그림 3. LMP7711 PSRR 다이어그램과 주파수에 대한 LP5900 LDO(Low Dropout) 리니어 레귤레이터 PSRR(▶별첨 그림3)

그림 4. 아날로그 신호 경로에서의 잡음/리플 감소를 위해 리니어 레귤레이터를 사용한 앰프 전력 공급(▶별첨 그림4)

저잡음 리니어 레귤레이터

애플리케이션에서 신호 경로 성능을 개선하는 한 가지 간단한 방법은 리니어 레귤레이터를 사용하여 신호 경로 IC에 전력을 공급하는 것이다. 리니어 레귤레이터는 필요한 전력 공급장치 레일을 생성하는 쉬운 방법을 제공하며, 전력 공급장치 라인에서 잡음/리플을 제거하는 이점을 가지고 있다. LP5900은 미국계 아날로그 반도체 제조사인 내셔널 세미컨덕터가 개발한 저잡음 리니어 레귤레이터 모델 중 하나로, 아날로그 및 RF 신호 경로의 IC에 전력을 공급하며, 저잡음 앰프, 전압 조절식 오실레이터(VCO) 및 RF 수신기와 기타 IC에 적용할 수 있다. 이 부품과 함께 올바른 회로 설계와 외장 커패시턴스 선택을 통해 신호 경로에서의 잡음/리플 성능을 효과적으로 개선할 수 있다.

이를 통해 25mA의 낮은 정적 전류로 출력 잡음이 업계 최저 수준으로 감소하며, 전력 공급장치 리플이 최대한 억제된다. LP5900 리니어 레귤레이터의 출력 잡음은 6.5mVRMS로 매우 낮다는 것이 특징이다. 또한 바이패싱 커패시터를 추가할 필요가 없으며, PSRR(전력 공급 제거비)가 75dB로 높다. 이 모델은 회로 보드에서 매우 작은 공간만을 차지하는 소형의 0.47mF 세라믹 커패시터 2개를 내장하고 있어 재료 비용을 절감할 수 있다. 또한 LP5900의 압력 강하는 80mV에 불과하여, 전압 조절식 전력을 제공하기 위해 매우 작은 전력 전압을 이용할 수 있게 된다. 최악의 경우에도, 출력 전압의 정확도가 ±3%를 초과하지 않으며, 출력 전류는 100mA에 이를 수 있다. VIN과 GND 사이에 가해지는 전압은 전압 출력(VOUT)보다 1V 이상 커야 한다. 최대 전압은 5.5V이고 최소 전압은 2.5V이다. GND를 기준 전압으로 하여 부하를 VOUT에 연결할 수 있다.

LP5900은 보드 공간을 절약하고 부품 수를 줄일 수 있도록 휴대용 애플리케이션에 맞게 특수 설계되었다. LDP(Low DropOut) 레귤레이터와 마찬가지로 LP5900 또한 안정적인 전압 공급을 위해 외부 커패시터가 필요하며, 이러한 커패시턴스에는 입력 커패시턴스 및 출력 커패시턴스가 포함된다. 최적의 성능을 얻으려면 올바른 선택이 필수이다. 커패시턴스를 선택할 때는 다음과 같은 요인을 고려해야 한다.

안정성을 높이기 위해 입력 커패시턴스는 출력 커패시턴스보다 크거나 같아야 하며, 0.47μF 커패시턴스를 적용하고 입력 핀과 접지 사이에 이 커패시턴스를 연결하는 것이 좋다. 특별한 설계를 통해 LP5900은 전압 출력쪽에서 소형 세라믹 커패시터 구현을 가능하게 한다. 애플리케이션 회로에서는 직렬 임피던스 범위가 5mΩ - 500mΩ인 커패시터(0.47μF - 10μF)를 적용하는 것이 적합하고, 커패시터는 VOUT 핀과 접지 사이에 연결해야 한다. 출력쪽에 탄탈 커패시터 또는 필름 커패시터를 적용할 수는 있지만 비용과 크기 문제가 있어 권장하지는 않는 것이 일반적이다. 출력 커패시턴스는 레귤레이터의 안정성을 보장하기 위해 최소 커패시턴스 값 요구 사항과 상응하는 직렬 임피던스(5mΩ - 500mΩ 범위)를 만족해야 한다. 또한 LP5900은 부하가 없는 상태에서 전압 조절 성능을 유지할 수 있다.

그림 5: LP5900의 전형적인 애플리케이션 구조 회로 다이어그램(▶별첨 그림5)

저작권©올포칩 미디어. 무단전재 및 재배포를 금지합니다.

- 엔엑스피 반도체 국내 디지털 무선전화기 시장 공략엔엑스피 반도체가 아날로그에서 디지털 테크놀로지로 빠르게 전환하고 있는 한국시장을 겨냥, LG-노텔과 노비타의 무선전화기에 탑재될 첨단 KDECT (Korean Digital Enhanced Cordless Telecommunications) 송수신 장치, UAA3547를 선보였다.

- 텍트로닉스 신세시스 리서치와 첨단 클럭 복구 장비 제공텍트로닉스가 신세시스 리서치(SyntheSys Research)와 첨단 클럭 복구 장비 제공을 위한 OEM 계약을 체결했다.

- 자일링스 ISE 소프트웨어 9.1i 출시로 FPGA 설계시간 대폭 단축자일링스는 업계에서 가장 폭넓게 사용되고 있는 자일링스의 설계 수트인 ISE™(Integrated Software Environment) 9.1i 버전을 출시했다. ISE는 현재 직면하고 설계 상의 주요한 이슈인 타이밍 클로저를 비롯해 생산성, 전력 문제 해결에 최적화되어 있다.

- 텐실리카 고속 기능형 시뮬레이터 TurboXim 출시텐실리카가 새로운 고속 기능형 시뮬레이터 TurboXim™를 출시했다. 이 제품은 텐실리카의 기존 cycle-accurate ISS (Instruction Set Simulator)보다 40 ~ 80배나 더 빠른 속도를 제공한다.

- 아테로스 PC 무선접속 강화를 위한 Bluetooth 2.1 + EDR 솔루션 발표아테로스, 업계 최초로 PC의 무선접속 강화를 위한 Bluetooth 2.1 + EDR 솔루션 발표

- 신플리시티 DSP 합성플랫폼 2006년 2배 이상 성장신플리시티는 지난 2006년 자사의 ESL(Electronic System Level: 전자시스템 레벨) 플랫폼인 신플리파이 DSP 통합 솔루션의 판매와 사용(in number of seats sold)이 2배 이상 증가했다고 발표했다.

- IEEE1588 타이밍 컨트롤을 가진 8-포트 스위치 개발 보드알테라, 내셔널세미컨덕터, MorethanIP 3社가 공동으로 IEEE1588 타이밍 컨트롤을 가진 최초의 8-포트 스위치 개발 보드를 발표했다.

- 삼성전자 시장기대치 상회하는 3분기 실적달성대내외적으로 불리한 시장 여건에도 불구하고 DRAM 및 LCD 패널 사업을 비롯해 전분야에서 고른 실적 호전에 힘 입어 삼성전자가 시장 기대치 1조9천억을 훨씬 뛰어넘는 2조원대의 3/4 분기 순이익을 달성했다. 삼성전자가 16일 열린 내외신 기자 간담회에서 발표한 지난 9월 30일 마감한 3/4분기 영업실적은 매출액 15조2천200억원에 순이익 2/4분기 대비 45% 증가한 2조1천800억 원이다.

- 멘토 그래픽스 EDA Tech Forum Keynote멘토 그래픽스가 지난 8월 30일 'EDA Tech Forum'을 개최했다. 이번 기술포럼에 참석한 멘토 그래픽스의 Walden C. Rhines 회장 & CEO는 'Changing the Design Rules'이라는 주제로 오픈 연설을 했다. 이번 포럼은 Funtional Verification, DFM, System Design, ESL, Automotive의 5개 트랙으로 진행되었다.

- 커넥선트 DVB-S2 시장의 절대 강자임을 입증커넥선트 시스템즈는 세계 최초의 DVB-S2 위성 셋톱박스 복조기 (Demodulator)와 순방향 오류 수정 (FEC: Forward Error Correction) 디코더의 누적 공급량이 100만 개를 돌파함으로써, DVB-S2 시장에서 커넥선트의 리더십이 다시 한 번 입증되었다고 발표했다.

- 스프린트 넥스텔 인텔 모토로라 및 삼성과 함께 4G 무선 광대역 이니셔티브 발표스프린트 넥스텔이 최초의 제 4세대(4G) 광대역 모바일 네트워크 개발 및 구축을 위해, 인텔, 모토로라 및 삼성과의 협력체제를 구축하고, 자사의 4G 무선 광대역 네트워크가 모바일 와이맥스 IEEE802.16e-2005 기술 표준을 사용하게 될 것이라고 발표했다.

- 인터내셔날 렉티파이어(IR) 2006 회계연도 4분기 실적 발표인터내셔날 렉티파이어(IR)는 6월 분기에 3억, 227만 달러의 매출과 3,380만 달러(또는 주당 0.47 달러)의 결산수익을 기록했다고 발표했다. 이와 비교해 지난 3월 분기에는 2억9,710만 달러의 매출과 2,810만 달러(또는 주당 0.39달러)의 결산수익을 기록했었다.

- CSR 상반기 최고 실적과 함께 2006년 전체적인 강세 전망CSR은 2006년 2분기를 포함한 상반기 실적을 발표하고, 해당 기간 전체의 수익과 영업이익률이 크게 증가하였다고 발표했다. CSR에서 올해 상반기에 선적된 제품의 개수가 모두 1억개로, 매출 규모가 지속적으로 증가하고 있다.

- ADI와 인텔 버스 인터페이스 SST 공동 발표아나로그디바이스(www.analog.com 한국 지사장: 전고영)는 세계최고의 실리콘 혁신 기업인 인텔과 공동으로 컴퓨터 시스템의 발열 및 전압 관리와 제어 정보를 효율적으로 통신하여 고성능 데스크톱 컴퓨터, 워크스테이션 및 서버의 성능과 안정성을 보호하는 새로운 방식을 공동 개발하고, 버스 인터페이스인 SST(Simple Serial Transport™)를 출시했다.

마이크로칩, 보안 기능을 확장한 maXTouch 터치스크린 컨트롤러 제품군 출시

마이크로칩, 보안 기능을 확장한 maXTouch 터치스크린 컨트롤러 제품군 출시 마우저, 2024년 1분기에 1만 종 이상의 신제품 추가

마우저, 2024년 1분기에 1만 종 이상의 신제품 추가 ST, 집약적 움직임 분석 지원하는 관성 모듈로 엣지-AI 센서 제품군 확장

ST, 집약적 움직임 분석 지원하는 관성 모듈로 엣지-AI 센서 제품군 확장 HMS 네트웍스, AGV를 위한 첨단 무선 기술 지원

HMS 네트웍스, AGV를 위한 첨단 무선 기술 지원 리미니스트리트 ‘2024 리미니스트리트 써밋’, 엔터프라이즈 소프트웨어 유지보수 혁신 지원

리미니스트리트 ‘2024 리미니스트리트 써밋’, 엔터프라이즈 소프트웨어 유지보수 혁신 지원

- ST, 2024 지속가능성 보고서 발표

- 마우저, IoT 및 에너지 하베스팅 설계 세미나 개최

- 매스웍스코리아, 다양한 분야의 AI 인재 발굴 위한 ‘제4회 매트랩 대학생 AI 경진대회’ 개최

- 다쏘시스템과 HD현대중공업, 버추얼 트윈 기반 설계-생산 일관화 통합 플랫폼 구축

- ams OSRAM과 도미넌트 옵토 테크놀로지스, 지능형 RGB LED로 스마트 자동차 실내 조명 구현

- 원프레딕트, 산업 AI 설비관리 솔루션으로 국제전기전력전시회 참가

그래픽 / 영상

지멘스 EDA, 최첨단 SoC 설계를 위한 혁신적인 에뮬레이션 및 프로토타이핑 솔루션 발표

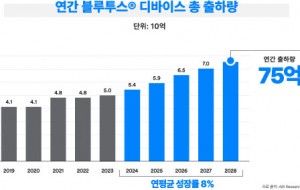

지멘스 EDA, 최첨단 SoC 설계를 위한 혁신적인 에뮬레이션 및 프로토타이핑 솔루션 발표 블루투스 지원 기기 출하량, 향후 5년 동안 연평균 8% 성장 전망

블루투스 지원 기기 출하량, 향후 5년 동안 연평균 8% 성장 전망 인터넷의 ‘필터 버블(Filter Bubble)’ 깨부수기

인터넷의 ‘필터 버블(Filter Bubble)’ 깨부수기

많이 본 뉴스

두산디지털이노베이션, 아시아 최대 보안 전시회서 사이버보안 솔루션 선보여

두산디지털이노베이션, 아시아 최대 보안 전시회서 사이버보안 솔루션 선보여 마이크로스트레티지 코리아, 정경후 신임 지사장 선임

마이크로스트레티지 코리아, 정경후 신임 지사장 선임 마우저 일렉트로닉스, 창립 60주년 맞이해

마우저 일렉트로닉스, 창립 60주년 맞이해 피커링, 80W의 스위치를 제공하는 고전력 시리즈 144 리드 릴레이 출시

피커링, 80W의 스위치를 제공하는 고전력 시리즈 144 리드 릴레이 출시 웨스턴디지털, ‘세계에서 가장 윤리적인 기업’ 6년 연속 선정

웨스턴디지털, ‘세계에서 가장 윤리적인 기업’ 6년 연속 선정 키사이트, 광대역폭 오실로스코프 프로브 출시

키사이트, 광대역폭 오실로스코프 프로브 출시 미르, AI 기반 자율이동로봇으로 혁신적인 팔레트 물류 자동화 지원

미르, AI 기반 자율이동로봇으로 혁신적인 팔레트 물류 자동화 지원 IAR, 임베디드 시스템 기능안전 인증 및 제품 개발 지원을 위한 FSG 컨소시엄 출범

IAR, 임베디드 시스템 기능안전 인증 및 제품 개발 지원을 위한 FSG 컨소시엄 출범 탈레스 알레니아 스페이스, 국내 최초 정찰위성 ‘425사업’ 위성의 성공적 발사 지원

탈레스 알레니아 스페이스, 국내 최초 정찰위성 ‘425사업’ 위성의 성공적 발사 지원 키사이트, AI 데이터센터 테스트 플랫폼 출시

키사이트, AI 데이터센터 테스트 플랫폼 출시