DSP(digital signal processing) 설계에 참여하고 있는 소프트웨어 엔지니어는 종종 시스템성능을 최대화하기 위한 이중 과제에 당면하게 된다. 대부분의 어플리케이션에서, 80/20 규칙이 적용되고 있는데 전체적인 시스템 성능을 증가시키는데 있어서, 시간이 많이 소요되고 오류가 발생하기 쉬우며 그리고 유지가 어려운 편인, 귀납적 알고리즘(recursive algorithm)에서 약 20퍼센트의 프로그램 코드가 최대 80퍼센트의 MIPS까지 차지하는 경우도 있다. 이 코드의 나머지 80퍼센트는 MIPS의 20퍼센트만을 소모할 뿐이지만 시스템 복잡성의 대부분을 차지한다. 소프트웨어 엔지니어의 두 가지 과제는 80퍼센트의 프로세싱 로드(소프트웨어의 20퍼센트)를 낮추는 한편, 또한 코드의 나머지 80퍼센트의 복잡성도 관리하는 것이다.

FPGA (Field programmable gate array) 코-프로세싱은 프로세싱 로드 절감에 있어 매우 뛰어난 솔루션을 제공한다. 그러나 이 방법의 장점을 취하려면 특정 시스템 설계가 코-프로세서를 추가하는 경우, 유리하게 될 지, 아니면 불필요한 복잡성만을 증가하는 것이 아닌지를 알 수 있도록, 체크해야 할 사항을 제대로 알고 있어야 한다.

Paul Ekas/ 수석 DSP 마케팅 부장 알테라 코퍼레이션

관련 첨부파일 : market_1022.doc

저작권©올포칩 미디어. 무단전재 및 재배포를 금지합니다.

- AA 배터리 타입 휴대기기의 전력설계

- 고전류 자동차 애플리케이션을 위한 전력제어 설계 방법론

- ADC의 성능을 높이는 몇가지 노하우

- Lattice FPGA ECP/EC를 이용한 PLL 구성

- 지그비(ZigBee)를 이용한 호텔 관리

- 통신 시스템을 위한 PPM의 중요성

- 프로그래머블 기술의 확장

- 크기 및 성능면에서 유리한 다위상 승압형 전원

- 전류 전송 로직(CTL):새로운 초저 전력 차동 인터페이스 기술 - 1부

- 적절한 저전력 고성능 고속 ADC의 선택

- 하이브리드 시대의 첨단 자동차 전력 기술

- OLED 디스플레이의 전원회로를 선택하는 효과적인 방법

- 비디오 프론트 엔드 및 백 엔드의 광대역 아날로그 비디오 스위치 설계

- SoC의 새로운 도전, 세계 최초의 멀티 플랫폼 FPGA

사피온, 텔레칩스에 AI 반도체 아키텍처 기반의 차량용 NPU IP 공급

사피온, 텔레칩스에 AI 반도체 아키텍처 기반의 차량용 NPU IP 공급 마우저, 가혹한 환경에서의 도전과제와 솔루션을 모색하는 최신 기술 리소스 허브 공개

마우저, 가혹한 환경에서의 도전과제와 솔루션을 모색하는 최신 기술 리소스 허브 공개 로지텍, 친환경 패션 브랜드 ‘플리츠마마’와 브랜드 콜라보 진행

로지텍, 친환경 패션 브랜드 ‘플리츠마마’와 브랜드 콜라보 진행 마이크로칩, 우주 애플리케이션 위한 내방사선 PolarFire SoC FPGA 출시

마이크로칩, 우주 애플리케이션 위한 내방사선 PolarFire SoC FPGA 출시 마우저, 미래의 엔지니어 및 혁신가 양성을 위해 Ten80 STEM 챌린지 후원

마우저, 미래의 엔지니어 및 혁신가 양성을 위해 Ten80 STEM 챌린지 후원

- 델 테크놀로지스, 사이버 복원력 강화한 데이터보호 어플라이언스 신제품 출시

- 테스트웍스, ETRI의 메타버스 개발 과제를 위한 3D 데이터 셋 구축 사례 공개

- 로지텍, 미니멀 라이프를 즐기자: ‘미니멀테리어’에 최적화된 추천 아이템 3

- 마이크로칩, 임베디드 보안 기능을 간단하게 통합할 수 있는 32비트 마이크로컨트롤러 출시

- 한국마이크로소프트, AI 기술의 미래 조명하는 ‘AI Tour in Seoul’ 개최

- 미루웨어, 국제인공지능대전(AI EXPO) 2024 참가

그래픽 / 영상

지멘스 EDA, 최첨단 SoC 설계를 위한 혁신적인 에뮬레이션 및 프로토타이핑 솔루션 발표

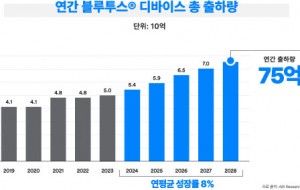

지멘스 EDA, 최첨단 SoC 설계를 위한 혁신적인 에뮬레이션 및 프로토타이핑 솔루션 발표 블루투스 지원 기기 출하량, 향후 5년 동안 연평균 8% 성장 전망

블루투스 지원 기기 출하량, 향후 5년 동안 연평균 8% 성장 전망 인터넷의 ‘필터 버블(Filter Bubble)’ 깨부수기

인터넷의 ‘필터 버블(Filter Bubble)’ 깨부수기

많이 본 뉴스

로데슈바르즈와 슬라롬, 5G 기반 증강현실 애니메이션 아바타 통화 실현

로데슈바르즈와 슬라롬, 5G 기반 증강현실 애니메이션 아바타 통화 실현 인텔 파운드리, 고개구율 극자외선(High-NA EUV) 도입으로 칩 제조 분야 선도

인텔 파운드리, 고개구율 극자외선(High-NA EUV) 도입으로 칩 제조 분야 선도 Qt그룹, 퀄컴과 협력해 산업용 IoT 기기 UI 개발 간소화

Qt그룹, 퀄컴과 협력해 산업용 IoT 기기 UI 개발 간소화 넥스페리아, 차세대 저전압 아날로그 스위치 출시

넥스페리아, 차세대 저전압 아날로그 스위치 출시 인텔, 한스 촹 아시아 태평양 지역 총괄 선임

인텔, 한스 촹 아시아 태평양 지역 총괄 선임 인텔, 세계 최대규모 뉴로모픽 시스템 공개

인텔, 세계 최대규모 뉴로모픽 시스템 공개 글로벌 300mm 팹 장비 투자액, 2025년 20% 증가

글로벌 300mm 팹 장비 투자액, 2025년 20% 증가 엔비디아 옴니버스, 차세대 데이터센터 구축 위한 디지털 청사진 공개

엔비디아 옴니버스, 차세대 데이터센터 구축 위한 디지털 청사진 공개 팔로알토 네트웍스, 박상규 지사장 선임

팔로알토 네트웍스, 박상규 지사장 선임 ST, 최첨단 온칩 디지털 서명 갖춘 NFC 태그로 브랜드 보호 확대

ST, 최첨단 온칩 디지털 서명 갖춘 NFC 태그로 브랜드 보호 확대