JNEye 링크 분석 툴을 이용함으로써 트랜시버 링크에 대해서 빠르게 시뮬레이션을 실시하고 채널 특성을 이해

Altera는 자사의 검증 및 보드 레벨 설계 툴 모음으로 JNEye 링크 분석 툴을 추가한다고 밝혔다. JNEye를 이용하면 설계 디자이너가 Altera FPGA 및 SoC의 고속 직렬 링크 성능을 빠르고 편리하게 평가할 수 있다. 이 툴은 통계적 링크 시뮬레이터의 속도와 시간 도메인 파형 기반 시뮬레이터의 정확도를 결합함으로써 새로운 하이브리드 동작 시뮬레이션 패러다임을 제공한다. JNEye 툴은 Altera의 10세대 제품 포트폴리오를 지원하도록 최적화되었으며 Altera의 차세대 FPGA 및 SoC의 트랜시버 링크 성능을 평가할 수 있는 플랫폼을 제공한다.

Altera의 펠로우 임원인 Mike Peng Li 박사는 “우리 회사는 고객들이 자사 시스템으로 Altera FPGA 및 SoC가 어떻게 동작할 것인지 빠르게 시뮬레이션 및 검증할 수 있도록 하기 위해서 포괄적인 유형의 시스템 레벨 설계 툴을 제공하고 있다. JNEye 링크 분석 툴은 이러한 솔루션으로서 가장 새롭게 추가되는 것이다. JNEye를 이용함으로써 디자이너들이 보드 레벨에서 트랜시버의 성능을 빠르게 파악할 수 있으며 Altera 디바이스가 고객 시스템에서 다른 디바이스들과 어떻게 상호동작할 것인지를 정확하게 이해할 수 있다”고 말했다.

JNEye 툴은 디바이스 특성분석 모델들을 결합해서 프로세스/전압/온도(PVT) 변동성을 정확하게 반영하도록 하는 하이브리드 모델링 기법을 제공한다. 이 툴은 여타의 산업표준 모델들을 이용해서는 달성할 수 없는 사실적인 시뮬레이션 정확도를 제공함으로써 직렬 링크 트랜시버 평가 작업을 간소화한다. JNEye는 IBIS-AMI 디바이스 모델을 이용한 링크 시뮬레이션을 지원하므로 Altera FPGA와 다른 트랜스미터 또는 리시버 사이의 직렬 링크를 평가하는 것이 가능하다.

JNEye 링크 분석 툴을 이용함으로써 디자이너가 목표로 하는 비트 오류율에 대해서 전송 및 수신 균등화 계수를 빠르게 최적화할 수 있다. 이 툴은 또한 디버그 및 검증을 지원하기 위한 설계 후 지원 툴로 이용할 수도 있다.

JNEye 툴은 Altera의 Quartus II 소프트웨어 환경 내에서 검증 및 보드 레벨 설계 툴 스위트에 포함되어서 제공된다. 이들 툴은 실제 세계 조건들로 시스템을 분석하고, 데이터를 해석하고, 시스템 성능을 모니터링할 수 있다. JNEye 툴은 현재 28nm Stratix V 및 Arria V FPGA와 20nm Arria 10 FPGA 및 SoC를 지원한다. 이 툴을 이용함으로써 설계 디자이너들이 Arria 10 디바이스를 가지고서 자신의 보드 시스템 디자인을 빠르게 검증할 수 있다.

가격 및 공급

JNEye 링크 분석 툴은 현재 다운로드할 수 있다. 이를 위해서는 Quartus II 소프트웨어 버전 13.1 가입자 버젼 라이선스를 필요로 한다. Altera Quartus II 소프트웨어의 연간 소프트웨어 가입 비용은 노드 한정 PC 라이선스로 2,995달러이며 Altera의 eStore또는 대리점에서 구입할 수 있다. 또한 JNEye 툴을 이용한 고속 링크 모델링 및 시뮬레이션에 대해서 설명하는 화이트 페이퍼를 제공하고 있다. 더 자세한 내용은 www.altera.com에서 볼 수 있으며, 현지 Altera 대리점으로 문의할 수 있다. (Axios 031-776-9888)

저작권©올포칩 미디어. 무단전재 및 재배포를 금지합니다.

- 인피니언의 보안 솔루션, 유럽 각국의 전자 신분증 및 온라인 공공 서비스에 채택온라인 쇼핑, 온라인 뱅킹, 온라인 채팅을 비롯해서, 오늘날 현대 사회는 온라인 상에서 물건을 구입하고, 의사소통을 하고, 정보를 공유한다. 온라인 상거래가 계속해서 증가하고 있을 뿐만 아니라 유럽에서는 온라인 공공 서비스 또한 빠르게 확대되고 있다.

ams의 고신뢰도 위치 센서 IC, 최신 능동형 섀시 제어 시스템에 정밀한 위치 데이터 제공ams는 고신뢰도의 비접촉 자기 위치 센서 기술을 통해 자동차 산업계의 수요에 부응하는 확고한 기반을 가졌다고 밝혔다. 세계적인 자동차 부품 공급업체인 콘티넨탈 (Continental )은 자사의 신형 CPS 시리즈 섀시 높이 센서를 ams의 자기 위치 센서인 AS5162를 통해 구현하고 있는 것으로 나타났다.

ams의 고신뢰도 위치 센서 IC, 최신 능동형 섀시 제어 시스템에 정밀한 위치 데이터 제공ams는 고신뢰도의 비접촉 자기 위치 센서 기술을 통해 자동차 산업계의 수요에 부응하는 확고한 기반을 가졌다고 밝혔다. 세계적인 자동차 부품 공급업체인 콘티넨탈 (Continental )은 자사의 신형 CPS 시리즈 섀시 높이 센서를 ams의 자기 위치 센서인 AS5162를 통해 구현하고 있는 것으로 나타났다. Altera, DesignCon 행사에서 FPGA 및 SoC의 탁월한 혁신성을 인정하는 상 수상Altera는 자사 FPGA 및 SoC 기술이 탁월한 혁신성을 인정 받아서 2014년 DesignCon 행사에서 2개 부문에 걸쳐 DesignVision 상을 수상했다고 밝혔다. Altera의 차세대 14nm Stratix 10 FPGA 및 SoC는 최우수 반도체 및 IP 부문을 수상했고, ARM® Development Studio 5(DS-5™) Altera Edition 툴키트는 최우수 설계 검증 툴 부문을 수상했다.

Altera, DesignCon 행사에서 FPGA 및 SoC의 탁월한 혁신성을 인정하는 상 수상Altera는 자사 FPGA 및 SoC 기술이 탁월한 혁신성을 인정 받아서 2014년 DesignCon 행사에서 2개 부문에 걸쳐 DesignVision 상을 수상했다고 밝혔다. Altera의 차세대 14nm Stratix 10 FPGA 및 SoC는 최우수 반도체 및 IP 부문을 수상했고, ARM® Development Studio 5(DS-5™) Altera Edition 툴키트는 최우수 설계 검증 툴 부문을 수상했다.  새로운 TITANBRITE LED 밝은 빛을 생산하는 동안 고전압 저전류 사용Lumex 는 TitanBrite 고-전압, 저-전류 LED, 고-성능 LED의 TitanBrite 패밀리의 새로운 추가 구성원의 글로벌 출시를 발표하였습니다. TitanBrite 고-접압, 저-전류 LED는 저 전류의 상태에서 고 전압을 사용할 수 있도록 대체 기술을 사용하였으며, 45% 이상의 보다 밝은 빛을 생산하며 뛰어난 배광을 제공합니다.

새로운 TITANBRITE LED 밝은 빛을 생산하는 동안 고전압 저전류 사용Lumex 는 TitanBrite 고-전압, 저-전류 LED, 고-성능 LED의 TitanBrite 패밀리의 새로운 추가 구성원의 글로벌 출시를 발표하였습니다. TitanBrite 고-접압, 저-전류 LED는 저 전류의 상태에서 고 전압을 사용할 수 있도록 대체 기술을 사용하였으며, 45% 이상의 보다 밝은 빛을 생산하며 뛰어난 배광을 제공합니다. 코그넥스, 휴대형 바코드 리더기 DataMan 8050 시리즈 출시코그넥스는 자사 제품 중 가장 빠르고 경제적인 산업용 휴대형 리더기, DataMan® 8050 시리즈를 출시했다. 혹독한 공장 조건을 견딜 수 있도록 견고한 하우징에 설계되고, 세계 최고로 꼽히는 코그넥스의 바코드 판독 알고리즘을 탑재한 DataMan 8050 시리즈는 까다로운 바코드도 빠르고 손쉽게 판독한다.

코그넥스, 휴대형 바코드 리더기 DataMan 8050 시리즈 출시코그넥스는 자사 제품 중 가장 빠르고 경제적인 산업용 휴대형 리더기, DataMan® 8050 시리즈를 출시했다. 혹독한 공장 조건을 견딜 수 있도록 견고한 하우징에 설계되고, 세계 최고로 꼽히는 코그넥스의 바코드 판독 알고리즘을 탑재한 DataMan 8050 시리즈는 까다로운 바코드도 빠르고 손쉽게 판독한다.- IDT의 20Gbps 인터커넥트 RapidIOIDT는 프로드라이브 테크놀로지(Prodrive Technologies)의 마더보드에 IDT의 20Gbps RapidIO 인터커넥트 디바이스가 사용되었다고 밝혔다. 이 마더보드는 2013년 4분기에 공표된 RTA(RapidIO Trade Association)의 데이터센터 표준 규격에 기반하여 제작되었다.

- 인피니언, 새로운 LTE LNA 및 LNA 뱅크 출시인피니언 테크놀로지스는 스마트폰의 데이터 전송 속도 향상을 위해 특별히 설계된 LTE 저잡음 증폭기(LNA) 및 Quad LNA 뱅크 시리즈를 출시했다. LTE(또는 4G)는 무선 통신을 위한 최신 표준으로 최대 300Mbit/s 데이터 전송 속도를 제공할 수 있다. 따라서 로딩 시간을 거의 체감하지 못할 정도로 빠른 모바일 인터넷 연결이 가능해 스마트폰 사용자의 편안한 사용감과 만족도를 크게 높여준다.

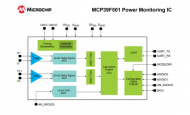

마이크로칩, 정확한 신호 포착 및 전력 계산 기능 갖춘 전력 모니터링 IC 출시마이크로컨트롤러, 아날로그 반도체 및 플래시-IP 솔루션 분야의 세계적인 리더인 마이크로칩테크놀로지가 새로운 전력 모니터링 IC인 MCP39F501을 출시했다고 밝혔다. 이 디바이스는 고집적 단상 전력 모니터링 IC로 실시간 AC 전력 측정을 위해 설계됐으며, 2개의 24 비트 델타-시그마 ADC, 16 비트 연산 엔진, EEPROM 및 유연한 2-와이어(two-wire) 인터페이스를 포함한다.

마이크로칩, 정확한 신호 포착 및 전력 계산 기능 갖춘 전력 모니터링 IC 출시마이크로컨트롤러, 아날로그 반도체 및 플래시-IP 솔루션 분야의 세계적인 리더인 마이크로칩테크놀로지가 새로운 전력 모니터링 IC인 MCP39F501을 출시했다고 밝혔다. 이 디바이스는 고집적 단상 전력 모니터링 IC로 실시간 AC 전력 측정을 위해 설계됐으며, 2개의 24 비트 델타-시그마 ADC, 16 비트 연산 엔진, EEPROM 및 유연한 2-와이어(two-wire) 인터페이스를 포함한다. - 마이크렐, 고전류 및 비절연 DC-DC 파워 서플라이를 위한 완벽한 기능의 고성능 디지털 PWM 컨트롤러 출시고성능 리니어 및 전력 솔루션을 비롯해 LAN, 타이밍 및 통신 솔루션 분야의 업계 선도주자인 마이크렐은 컴퓨팅 및 텔레콤 애플리케이션의 고전류, 비절연 DC-DC 파워 서플라이를 위한 트루-디지털 PWM 컨트롤러 MIC21000을 출시했다.

- 안리쓰, 세계 최초의 40GHz 핸드헬드 케이블 및 안테나 애널라이저 출시안리쓰는 최대 40GHz의 주파수 도달범위를 갖춘 세계 최초의 핸드헬드 케이블 및 안테나 애널라이저인 마이크로웨이브 (Microwave) Site Master S820E를 출시했다고 밝혔다. 이로써 안리쓰가 최초의 광대역 Site Master 를 출시한 이래 지난 15년 동안 핸드헬드 애널라이저 시장에 쌓아 올린 리더십 지위를 더욱 확고하게 다질 수 있게 되었다.

- 텍트로닉스, 자동 HDMI 2.0 적합성 테스트, 디버그 솔루션 발표텍트로닉스는 최근 릴리스된 HDMI 2.0 사양을 위한 완전 자동 적합성 테스트 및 디버그 솔루션을 발표했다. 이 솔루션은 빠르고 일관적이고 정확한 테스트 결과를 위한 HDMI 2.0 트랜스미터 테스트와Direct Synthesis 기반 리시버 테스트, 케이블 테스트 요구 사항을 충족한다.

- 리니어, 80V 동기식 SEPIC/ 인버팅/ 부스트 DC/DC 컨트롤러 출시리니어 테크놀로지 코리아는 자사 최초의 동기식 SEPIC, 인버팅, 부스트 및 플라이백 멀티 토폴로지 DC/DC 컨트롤러 (제품명: LT8710)를 출시했다고 밝혔다. 이 동기식 디바이스는 출력 다이오드를 고효율 P채널 MOSFET으로 대체시켜, 효율성, 최대 출력 전류 (최고 10A)를 증가시키고, 고전력 애플리케이션으로 중간에서 일반적으로 요구되는 히트 싱크를 제거한다.

- Xilinx, 업계 유일의 하이엔드 20나노 제품군인 첫 버텍스 울트라스케일 올 프로그래머블 디바이스 개발 완료자일링스는 또 다시 업계 최초로 20나노에서 첫 버텍스(Virtex)® 울트라스케일(UltraScale)™ 디바이스를 개발 완료했다고 발표했다. 울트라스케일 아키텍처에 기반한 업계 유일의 하이엔드20나노 제품인 버텍스 울트라 스케일 제품군은 여러 가지 다양한 애플리케이션을 위해 유례 없는 성능과 시스템 통합, 대역폭을 제공하고 있다.

- TI, 업계에서 가장 정밀한 측정 능력을 제공하는 산업용 애플리케이션을 위한 연산 증폭기 출시TI(대표 이사 켄트 전)는 오토-제로(auto-zero) 기법을 이용하지 않고도 정밀한 오프셋 전압 및 드리프트를 달성하는 업계 최초의 36V 레일-투-레일 입력/출력(RRIO) 연산 증폭기를 출시한다고 밝혔다. OPA192는 전체 온도 범위에 걸쳐서 안정적인 오프셋 전압 드리프트를 달성하기 때문에 시스템 차원의 교정이 필요 없다.

슈나이더 일렉트릭, HMS 네트웍스로부터 1천만 번째 Anybus 모듈상 수상

슈나이더 일렉트릭, HMS 네트웍스로부터 1천만 번째 Anybus 모듈상 수상 ASML 코리아, WISET과 함께 하는 ‘글로벌 멘토링’ 성료

ASML 코리아, WISET과 함께 하는 ‘글로벌 멘토링’ 성료 지멘스, 올림피아 익스프레스 커피 머신 설계 및 생산 현대화 지원

지멘스, 올림피아 익스프레스 커피 머신 설계 및 생산 현대화 지원 어플라이드 머티어리얼즈, ‘넷제로 2040 플레이북’ 진척 상황 공유

어플라이드 머티어리얼즈, ‘넷제로 2040 플레이북’ 진척 상황 공유 바이코, AID 2024에서 48V 존 아키텍처를 위한 혁신적인 모듈형 솔루션 발표 예정

바이코, AID 2024에서 48V 존 아키텍처를 위한 혁신적인 모듈형 솔루션 발표 예정

- 쿤텍, 자체개발 솔루션 ‘이지스(AEGIS)’ 통해 SW 공급망 보안 가이드라인 준수 지원

- 로지텍, 휠라 본사 오피스에 스마트 워크플레이스 솔루션 구축

- 지멘스, 3D IC 설계, 검증 및 제조를 위한 통합 콕핏 솔루션 출시

- 다쏘시스템, VLP앤파트너스에 3D익스피리언스 공급

- 비쉐이, 효율성과 신뢰도를 향상시키는 3세대 1200V SiC 쇼트키 다이오드 출시

- 로데슈바르즈, 무선 통신을 위한 AI 잠재력을 실현하기 위해 AI-RAN 얼라이언스에 합류

그래픽 / 영상

많이 본 뉴스

CGD, 향상된 열 성능을 갖춘 새로운 GaN 전력 IC 패키지 발표

CGD, 향상된 열 성능을 갖춘 새로운 GaN 전력 IC 패키지 발표 LG전자- Qt그룹, ’차량용 webOS 콘텐츠 플랫폼’ 구축을 위해 협력

LG전자- Qt그룹, ’차량용 webOS 콘텐츠 플랫폼’ 구축을 위해 협력 디지키, ‘스마트 세상에서의 AI’를 다룬 시티 디지털 시즌 4 동영상 시리즈 발표

디지키, ‘스마트 세상에서의 AI’를 다룬 시티 디지털 시즌 4 동영상 시리즈 발표 TI, 더 작고 에너지 효율적인 고전압 모터를 위한 업계 최초 GaN IPM 공개

TI, 더 작고 에너지 효율적인 고전압 모터를 위한 업계 최초 GaN IPM 공개 조시큐리티, 악성코드 정밀 분석 솔루션 조샌드박스 V40 ‘토르말린’ 출시

조시큐리티, 악성코드 정밀 분석 솔루션 조샌드박스 V40 ‘토르말린’ 출시 로데슈바르즈, 최대 2GHz 대역을 지원하는 세계 최소형 오실로스코프 ‘MXO 5C’ 시리즈 출시

로데슈바르즈, 최대 2GHz 대역을 지원하는 세계 최소형 오실로스코프 ‘MXO 5C’ 시리즈 출시 전 세계 반도체 재료 시장, 2023년 전년 대비 8.2% 하락

전 세계 반도체 재료 시장, 2023년 전년 대비 8.2% 하락 로옴의 투인원 SiC 몰드 타입 모듈, xEV용 인버터 소형화에 기여

로옴의 투인원 SiC 몰드 타입 모듈, xEV용 인버터 소형화에 기여 NCH코리아, 분말형 세척제 ‘스필 드래곤’ 출시

NCH코리아, 분말형 세척제 ‘스필 드래곤’ 출시 테스트웍스, ETRI의 메타버스 개발 과제를 위한 3D 데이터 셋 구축 사례 공개

테스트웍스, ETRI의 메타버스 개발 과제를 위한 3D 데이터 셋 구축 사례 공개

자동차 애플리케이션을 위한 안전한 블루투스 LE 연결

자동차 애플리케이션을 위한 안전한 블루투스 LE 연결 헤드셋 매출의 향방, 하락세는 지속할 것인가?

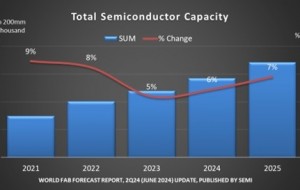

헤드셋 매출의 향방, 하락세는 지속할 것인가? 한국 반도체 생산능력, 올해 첫 5백만장 넘어선다

한국 반도체 생산능력, 올해 첫 5백만장 넘어선다