단 패키징 우수 센터는 어플라이드머티어리얼즈와 마이크로일렉트로닉스 연구소가 공동으로 1억 달러를 출자하여 설립했다. 이 세계적 수준의 기관은 초청정 공간을 유지하기 위한 약 393평(14,000 ft²) 크기의 Class-10 클린룸을 기반으로, 반도체 산업의 주요 성장동력인 3D 칩 패키징 연구 개발을 위한 300mm의 완전 통합형 제조 시스템을 갖추고 있다.

본 센터는 웨이퍼 수준 패키징(Wafer Level Packaging: WLP) 기술 개발을 위해 설립된 첫 전용 연구 시설로, 어플라이드머티어리얼즈의 최첨단 장비 및 공정 기술과 3D 칩 패키징 분야에 있어 최고를 자랑하는 마이크로일렉트로닉스 연구소의 연구 역량이 결합될 예정이다.

마이클 스플린터(Michael R. Splinter) 어플라이드머티어리얼즈 CEO 겸 이사회 의장은 “첨단 패키징 우수 센터의 설립은 아시아에서 신제품 개발 능력을 향상시킬 수 있는 계기”라고 밝히며, “본 센터를 설립함으로써 신기술 개발 및 역량 강화를 실현하여, 아시아 지역의 파트너들과 보다 긴밀한 비즈니스를 구축해 나갈 것이다.”라고 말했다.

마이크로일렉트로닉스 연구소의 사무총장인 딤리 궝(Dim-Lee Kwong) 교수는 “첨단 패키징 우수 센터의 설립은 반도체 산업을 이끌어가는 파트너 간의 전략적 협력을 보여주는 좋은 사례이며, 혁신적인 웨이퍼 수준 패키징 기술 개발을 촉진시켜 전 세계적으로 이 기술이 적용될 수 있도록 할 것이다.”라 말하며, “이번 협력을 통해 반도체 산업 전반에 걸쳐 3D 칩 패키징 기술의 채택이 가속화 될 것”이라고 덧붙였다.

지금까지 반도체 칩은 테두리에 있는 와이어를 통해 패키지와 연결되어 왔다. 이러한 패키징 방식은 칩 연결고리(connections)의 개수에 한계를 가져올 뿐 아니라, 긴 와이어로 인한 신호 속도의 지연 및 전력의 비효율화를 야기한다. 그러나 3D 칩 패키징의 경우 실리콘 관통전극(Through-silicon-vias: TSVs)을 통해 여러 개의 칩을 차곡차곡 쌓을 수 있으며, 칩 더미(스택, stack)를 수직으로 잇는 와이어를 통해 연결할 수 있다. 이 기술은 로직 칩(logic chip) 위에 메모리 칩을 쌓아 올리는 공정 시 패키지 사이즈를 35%까지, 전력 소비량을 50%까지 줄여주며, 데이터 대역폭은 8배 이상 증가시킨다.

어플라이드머티어리얼즈와 마이크로일렉트로닉스 연구소 간의 연구 협력을 위해 설립된 첨단 패키징 우수 센터는 공정 및 통합, 하드웨어 개발 등 독립적인 연구를 위해서도 사용될 예정이다. 본 센터에서 이미 50명이 넘는 연구진이 연구 활동을 펼치고 있다.

관련 링크 : http://www.appliedmaterials.com/

저작권©올포칩 미디어. 무단전재 및 재배포를 금지합니다.

- 싸이프레스, EZ-USB® FX3™ USB 3.0 컨트롤러를 위한 그래픽 소프트웨어 툴 발표싸이프레스 코리아 (지사장 임영도 www.cypress.com)는 SuperSpeed USB 3.0을 위한 EZ-USB® FX3 컨트롤러용 GPIF™ II 디자이너 소프트웨어를 즉시 활용할 수 있다고 발표했다.

- 에머슨 네트워크 파워, 최신 ATCA 블레이드로 새로운 성능 표준 수립에머슨의 사업부이자 Business-Critical Continuity™ 구현을 선도하는 글로벌 리더, 에머슨 네트워크 파워(Emerson Network Power)가 오늘(2012년 3월 8일) 출시한 고성능 서버 블레이드는 ATCAⓇ(AdvancedTCAⓇ) 기반 텔레콤 서버 설계자들이 사용할 수 있는 처리, 메모리 및 I/O 기능을 확장하여 가장 까다로운 제어 평면 애플리케이션을 지원한다.

- 코아로직, 2011년 실적 발표코아로직 (서광벽 대표)은 3월 7일 공시를 통해 2011년도 영업 실적을 발표했다. 2011년도의 매출액 427억원과 영업이익 10억원은 전년과 비교하여 각각 217억원과 171억원씩 증가한 수치이다. 특히 전년 대비 무려 104%의 성장을 기록한 영업이익은 2007년 이후 3년만에 흑자로 전환된 기록이다.

- 브릿지룩스-셰브론, 캘리포니아 도시들과 이노베이티브 거리조명 이니셔티브(ISI) 전개셰브론 에너지 솔루션(Chevron Energy Solutions)과 브릿지룩스(Bridgelux)는 도시의 에너지 및 유지보수 비용을 크게 낮출 수 있도록 LED 조명 기술에 있어서 혁신적 발전을 장려하기 위한 연합을 결성했다고 밝혔다.

- 마이크로칩, 소형 패키지의 저가형 32비트 PIC32 마이크로컨트롤러 제품군 확장마이크로칩 테크놀로지(한국 대표: 한병돈)는 오늘(2012년 3월 8일) 독일에서 열린 임베디드 월드 컨퍼런스(Embedded World Conference)에서 핀 수가 적은 새로운 32비트 PIC32 마이크로컨트롤러(MCU) 제품군을 새롭게 선보였다.

- 리니어 테크놀로지, 마이크로파워 푸시버튼 온/오프 컨트롤러 출시리니어 테크놀로지 코리아(대표 홍사곽)는 푸시버튼 인터페이스 또는 서플라이 공급을 통해 1.5V ~ 36V의 시스템 전력을 관리할 수 있는 푸시버튼 온/오프 컨트롤러(제품명: LTC2955)를 개발했다고 밝혔다.

- 프리스케일, 보티카(VortiQa) 네트워킹 소프트웨어 확장프리스케일 반도체(www.freescale.com)는 자사의 성공적인 보티카(VortiQa) 네트워킹 소프트웨어 제품군의 기능을 기존 보안 및 네트워킹을 넘어선 영역으로 확장하고 있다. 프리스케일의 최첨단 코어아이큐(QorIQ) 및 코어아이큐(QorIQ) 컨버지(Qonverge) 제품용 임베디드 소프트웨어의 개발 속도를 단축하고 성능을 높이기 위해 프리스케일은 리눅스(Linux®) 사용자 공간에서 프로그래밍을 지원하는 업계 최초의 포괄적인 임베디드 네트워킹 소프트웨어 프레임워크인 보티카(VortiQa™) 플랫폼 서비스 패키지(PSP)를 발표했다.

- 아나디직스, 2012 China ACE 어워드 수상아니디직스(ANADIGICS, Inc., 한국대표: 김경민)는 오늘(2012년 3월 5일), 제 17회 IIC-China(International IC-China Conference & Exhibition)와 함께 거행된 리셉션에서 2012 China ACE(Annual Creativity in Electronics) 어워드를 수상했다고 발표했다. 아나디직스의 4세대 고효율 저전력(HELP4™) 전력 증폭기(PA) ALT6738는 2012 China ACE RF/무선 제품상을 수상하는 영예를 안았다.

- 싸이프레스, PSoC Creator 2.0 설계 환경을 위한 "컴포넌트 팩" 업데이트 발표 !싸이프레스 코리아 (지사장 임영도 www.cypress.com)는 자사의 PSoC 3과 PSoC 5 프로그래머블 시스템-온-칩 (programmable system-on-chip) 제품군을 위한 탁월한 PSoC Creator™ 설계 환경의 2.0 버전에 확대 기능을 발표했다.

- 실리콘랩, 유연하고 개발자 친화적인 32비트 혼합신호 MCU 발표실리콘랩(Silicon Laboratories Inc., 지사장 이종찬)은 오늘(2012년 3월 6일), 32비트 시장에 전례 없는 설계 유연성을 제공하는 새로운 Precision32™ 마이크로 컨트롤러(MCU) 제품군을 발표했다.

- 프리스케일, 익스트린직(Xtrinsic) 전자컴파스 소프트웨어 발표프리스케일 반도체(www.freescale.com)는 오늘(2012년 3월 6일) 프리스케일 익스트린직(Xtrinsic) 가속도계 및 자력계와 함께 고도로 정확한 자기장 데이터를 제공하는 새로운 센서 융합 솔루션, 익스트린직(Xtrinsic) 전자컴파스(eCompass) 소프트웨어를 발표했다.

- AMD, 라데온™ HD 7800 시리즈 그래픽으로 업계 리더십 강화AMD는 오늘(2012년 3월 6일) 28nm 공정의 세번째 시리즈인 AMD 라데온(Radeon™) HD 7870 GHz 에디션 및 AMD 라데온(Radeon™) HD 7850 그래픽 카드를 출시했다.

- 커넥선트, 모바일 애플리케이션을 위한 저전력 HD 오디오 코덱 출시커넥선트 시스템즈 (한국지사장: 박경배)는 노트북, 울트라북, 태블릿 등 모바일 PC에 고품질 오디오를 제공하기 위한 저전력 HD 오디오 코덱인 CX20752와 CX20754를 출시했다고 밝혔다.

- ADI, 자일링스의 FPGA 타깃 디자인 플랫폼 지원하는 FMC 보드 출시아나로그디바이스(www.analg.com)는 자일링스(Xilinx Inc.)의 새로운 28nm 7 시리즈 FPGA(Field Programmable Gate Array) 평가키트에 연결되는 데이터 컨버터 FMC 보드(FPGA 메자닌 카드[Mezzanine Card]) 2종을 선보였다.

사피온, 텔레칩스에 AI 반도체 아키텍처 기반의 차량용 NPU IP 공급

사피온, 텔레칩스에 AI 반도체 아키텍처 기반의 차량용 NPU IP 공급 마우저, 가혹한 환경에서의 도전과제와 솔루션을 모색하는 최신 기술 리소스 허브 공개

마우저, 가혹한 환경에서의 도전과제와 솔루션을 모색하는 최신 기술 리소스 허브 공개 로지텍, 친환경 패션 브랜드 ‘플리츠마마’와 브랜드 콜라보 진행

로지텍, 친환경 패션 브랜드 ‘플리츠마마’와 브랜드 콜라보 진행 마이크로칩, 우주 애플리케이션 위한 내방사선 PolarFire SoC FPGA 출시

마이크로칩, 우주 애플리케이션 위한 내방사선 PolarFire SoC FPGA 출시 마우저, 미래의 엔지니어 및 혁신가 양성을 위해 Ten80 STEM 챌린지 후원

마우저, 미래의 엔지니어 및 혁신가 양성을 위해 Ten80 STEM 챌린지 후원

- 델 테크놀로지스, 사이버 복원력 강화한 데이터보호 어플라이언스 신제품 출시

- 테스트웍스, ETRI의 메타버스 개발 과제를 위한 3D 데이터 셋 구축 사례 공개

- 로지텍, 미니멀 라이프를 즐기자: ‘미니멀테리어’에 최적화된 추천 아이템 3

- 마이크로칩, 임베디드 보안 기능을 간단하게 통합할 수 있는 32비트 마이크로컨트롤러 출시

- 한국마이크로소프트, AI 기술의 미래 조명하는 ‘AI Tour in Seoul’ 개최

- 미루웨어, 국제인공지능대전(AI EXPO) 2024 참가

그래픽 / 영상

지멘스 EDA, 최첨단 SoC 설계를 위한 혁신적인 에뮬레이션 및 프로토타이핑 솔루션 발표

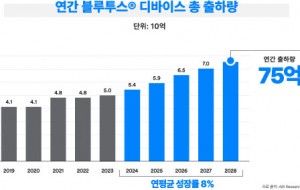

지멘스 EDA, 최첨단 SoC 설계를 위한 혁신적인 에뮬레이션 및 프로토타이핑 솔루션 발표 블루투스 지원 기기 출하량, 향후 5년 동안 연평균 8% 성장 전망

블루투스 지원 기기 출하량, 향후 5년 동안 연평균 8% 성장 전망 인터넷의 ‘필터 버블(Filter Bubble)’ 깨부수기

인터넷의 ‘필터 버블(Filter Bubble)’ 깨부수기

많이 본 뉴스

마우저, ‘2024 미래를 여는 설계 콘테스트’ 후원

마우저, ‘2024 미래를 여는 설계 콘테스트’ 후원 TI, 임베디드 월드2024에서 스마트하고 지속 가능한 미래를 위한 기술 소개

TI, 임베디드 월드2024에서 스마트하고 지속 가능한 미래를 위한 기술 소개 IMDT, AI 기반 비전 애플리케이션에 최적화된 새로운 SOM 및 SBC 출시

IMDT, AI 기반 비전 애플리케이션에 최적화된 새로운 SOM 및 SBC 출시 NCH코리아, 산업 윤활관리 프로그램 런칭

NCH코리아, 산업 윤활관리 프로그램 런칭 베트남 토요타, 시놀로지 데이터 관리 시스템 채택해 비즈니스 복원력 강화

베트남 토요타, 시놀로지 데이터 관리 시스템 채택해 비즈니스 복원력 강화 미르, AI 기반 자율이동로봇으로 혁신적인 팔레트 물류 자동화 지원

미르, AI 기반 자율이동로봇으로 혁신적인 팔레트 물류 자동화 지원 쿤텍-시큐어아이씨, 임베디드 분야 보안 강화 지원하는 파트너십 체결

쿤텍-시큐어아이씨, 임베디드 분야 보안 강화 지원하는 파트너십 체결 어플라이드 머티어리얼즈 코리아, 4년 연속 ‘우리 하천 지킴이 활동’ 지원

어플라이드 머티어리얼즈 코리아, 4년 연속 ‘우리 하천 지킴이 활동’ 지원 콩가텍, µATX 서버 캐리어 보드 및 최신 인텔 제온 프로세서 기반 모듈형 에지 서버 생태계 확장

콩가텍, µATX 서버 캐리어 보드 및 최신 인텔 제온 프로세서 기반 모듈형 에지 서버 생태계 확장 델 테크놀로지스, 2024년 AI 시대를 위한 광범위한 클라이언트 신제품 공개

델 테크놀로지스, 2024년 AI 시대를 위한 광범위한 클라이언트 신제품 공개