이번에 개발된 제품은 512Mb(Mega bit: 메가 비트) DDR2 D램을 4개

적층한 2Gb 대용량 D램 적층칩과 4GB(Giga Byte: 기가 바이트) 모듈이다.

WSP 기술은 기존 패키지 방식인 MCP(Multi Chip Package)에 비해 패키지

사이즈는 소형화하고, 용량/스피드/저소비전력 등 성능은 대폭 개선할 수

있는 최첨단 복합칩 기술이다.

WSP(Wafer-Level Processed Stack Package)는 칩을 수직 관통하는 홀(Hole)을

통해 "칩間 직접 접속"하는 패키지 방식으로, 칩 상하間 별도의 간격이나 와이어

연결을 위한 공간이 불필요함에 따라 패키지 크기를 줄이고 성능을 높일 수 있다.

삼성전자는 작년 4월, 이 기술을 세계 최초로 낸드플래시 메모리에 적용했으며

이번에 D램에도 세계 최초로 적용하여 기존 기술을 적용한 D램 패키지 대비

면적은 15%, 두께는 50% 이상 축소했다.

낸드플래시에 이 기술을 적용하는 경우에는 회로가 없는 주변 영역에 관통전극을

형성하고 재배선을 이용하여 연결을 했지만 D램의 경우 제품 특성상 고속 동작이

요구되어 재배선을 할 경우 속도 저하가 발생되는 어려움이 있었다.

이에 삼성전자는 D램 칩 중앙부의 회로가 있는 부분에 관통전극을 직접 형성하고

이에 따른 공정상의 어려움을 극복함으로써 차세대 고속 D램 모듈 구현을 위한

핵심 기술을 확보하였다.

향후 차세대 D램 제품이 시장에 본격 상용화 되면, 기존의 칩 적층 기술로는 앞서

언급한 재배선에 의한 속도 저하 문제로 1.6Gb/초 수준의 데이터 처리가 어려울 것으로

예상되나 삼성전자는 이번에 적용 성공한 WSP 기술을 통해 그 한계를 극복 할 수 있을

것으로 전망된다.

또한 D램의 경우 낸드보다 회로가 복잡하게 형성되어 있어 웨이퍼를 박막화 할 경우

웨이퍼 휨 현상(Warpage)이 더욱 잘 발생하는데 삼성전자는 작년 11월에 개발 성공한

16단 MCP 패키지에 적용된 웨이퍼 박막화 기술을 활용하여 이를 극복할 수 있었다.

시스템에 적용되는 반도체의 고성능화를 위해서는 단품 칩 개발도 중요하나, 수십 나노

수준까지 축소된 칩 가공 기술을 뒷받침 할 수 있는 패키지 기술의 개발 역시 수반되어야

한다.

지금까지는 패키지 기술이 칩 제조 기술만큼 빠른 속도로 진화하지 못하였기

때문에, 나노급까지 진화된 칩 제조 기술과 마이크로미터급의 패키지 기술간의 격차가

발생해 왔었다.

이와 관련하여, 삼성전자가 주도하고 있는 차세대 패키지인 기술인 WSP는 칩 제조

기술과 패키지 기술간의 미세화 격차를 줄일 수 있는 해법이 될 수 있을 것으로 기대된다.

저작권©올포칩 미디어. 무단전재 및 재배포를 금지합니다.

- 캐털리스트 500mA의 LDO 레귤레이터캐털리스트 세미컨덕터는 LDO 레귤레이터를 새로이 출시했다. CAT6219 LDO 레귤레이터는 아주 작은 5 핀의 얇은 SOT-23 패키지, 1mm 높이에 출력 전력 500mA 피크를 제공한다.

- NS 최저 수준의 전력 소모 고속 콤패레이터 제품군 출시내셔널 세미컨덕터 코리아는 전파 지연이 서브 나노세컨드(700 ps) 수준이면서 전력 소비가 업계 최저(공칭 21 mA)인 듀얼 콤패레이터 LMH7322를 출시한다고 발표했다.

- 샌디스크- 키몬다 MCP 공동 개발 발표키몬다 코리아는 샌디스크와 키몬다가 샌디스크의 낸드 플래시메모리와 컨트롤러, 키몬다의 저전력 모바일 DRAM을 이용한 MCP를 공동 개발 및 제조한다고 발표했다.

- IDT 저전력 ‘AMB 플러스’ 출시IDT는 자사의 AMB (Advanced Memory Buffer) 제품군의 새로운 3세대 디바이스인 ‘AMB 플러스(AMB+)’를 선보였다. ‘AMB 플러스’는 업계의 다른 AMB 제품 대비 최대 40%의 전력 절감 효과가 있어 업계에서 가장 낮은 전력 소모 수준을 자랑한다.

- 기존 SRAM 대체 4Mb 비휘발성 FRAM 탄생FRAM의 앞선 신뢰성과 속도를 경쟁력으로 기존 SRAM 시장 진입을 노리고 있는 램트론이 업계 최초로 비휘발성 4Mb FRAM 메모리(FM22L16)를 개발했다.

- 알테라 인텔의 FSB를 위한 FPGA 기반 가속기 지원 발표알테라는 익스트림데이터(XtremeData)社가 인텔의 FSB(Front Side Bus)를 지원하는 자사의 XD2000i 플러그-호환 FPGA 코프로세서 모듈에 고성능 Stratix® III FPGA를 채택했다고 발표했다. 오늘 발표된 고성능 컴퓨팅 솔루션은 인텔의 Xeon 프로세서 기반 서버의 프로세싱 성능을 높여주는 모듈로, 듀얼 또는 쿼드 소켓 서버의 프로세서 소켓에 직접 꽂을 수 있다. 이로 인해 프로세서만 사용할 때와 비교해 어플리케이션의 속도를 10배에서 100배까지 빠르게 하는 동시에, 전체 시스템의 소비 전력을 줄여준다.

- 2.5G 및 3G 모바일 통신 보안 MCU 포트폴리오 확장ST마이크로일렉트로닉스는 고용량 2.5G 및 3G (3세대) 휴대폰 SIM 카드를 위해 고안된 새로운 보안 마이크로컨트롤러 2종을 출시하였다. ST21Y036 및 ST21Y144는 각각 36 Kbytes 및 144 Kbytes의 사용자 EEPROM을 제공하며, 2006년말에 출시되어 이미 양산중인 ST21Y0068과 함께 새롭게 보안 MCU 포트폴리오에 추가된 제품이다. 최대 16-Mbytes의 리니어 어드레싱 기능을 갖춘 향상된 8/16-bit CPU 코어에 기반한 이 제품군은 고용량, 빠른 리드타임 및 가격 경쟁력을 위해 업계에서 요구하는 조건을 충족시키는 최첨단 0.13-미크론 EEPROM 기술로 생산되었다.

- 마이크로칩 전세계 8비트 마이크로컨트롤러 업계의 매출 1위 기록시장조사업체인 가트너 데이터퀘스트(Gartner Dataquest)의 2006년 순위 발표에 따르면, 세계적인 마이크로컨트롤러 및 아날로그 반도체 전문업체인 마이크로칩 테크놀로지(한국 지사장: 한병돈)가 전세계 8비트 마이크로컨트롤러 매출 부문에서 1위를 기록한 것으로 나타났다. 마이크로칩은 매출 부문에서 1위를 차지하며 전세계 8비트 마이크로컨트롤러 시장을 선도하게 된 것은 물론, 2002년에 달성했던 단위 출하량 1위 자리도 탈환하게 되었다. 또한 마이크로칩은 이번 분기에 20억 번째 플래시 마이크로컨트롤러를 출하하게 될 것으로 기대하고 있다.

- 자일링스 새로운 저가격 스파르탄-DSP 시리즈 출시세계적인 프로그래머블 로직 솔루션 공급업체인 자일링스는 DSP애플리케이션을 위해 XtremeDSP™ 솔루션을 획기적으로 확장함으로써 새로운 수준의 가격과 성능, 전력 특성을 구현한 저가격의 스파르탄(Spartan™)-DSP 시리즈를 출시하고 개발 보드 및 향상된 설계 소프트웨어와 함께 공급한다고 밝혔다. FPGA업계에서 가장 낮은 비용으로 최고의 DSP 성능을 제공하는 스파르탄-DSP 시리즈는 미화 30달러 미만으로 20GMAC을 구현할 수 있으며, 비슷한 수준의 DSP 성능을 제공하는 다른 FPGA와 비교해 동적 전력소모는 최대 50%까지 절감할 수 있다.

- 프리스케일 ColdFire® 제품군의 USB 옵션 확대가전 분야의 주류를 이루고 있는 USB(Universal Serial Bus) 기술이 산업 분야의 표준으로 급속하게 부각되고 있다. 이에 프리스케일 세미컨덕터(www.freescale.com)는 광범위한 산업 분야의 적극적인 대응을 위해 유연한 USB 연결 기능을 제공하는 32비트 ColdFire® USB 디바이스 제품군을 새롭게 확장하고 설계자들에게 다양한 시장 기회에 대응하도록 지원하고 있다.

- 인텔 시스템 온 칩 프로세서로 가동되는 새로운 세대의 가전제품가전제품 시장을 공략하기 위해 고도로 집적된 미디어 프로세서가 디지털 셋톱 박스 및 네트워킹 미디어 플레이어와 같은 새로운 세대의 기기에 사용되며, 소비자들에게 고급화된 가정 내 정보 및 엔터테인먼트 서비스를 소비자들에게 제공하게 된다.

- 멀티-포맷 방송용 라우터에 알테라 Stratix II GX FPGA 채택알테라의 Triple-Rate SDI 개발 키트를 이용해 엔지니어링 생산성 대폭 향상 알테라은 해리스(Harris)가 최근에 발표한 Platinum™ 비디오 방송 라우터 제품라인의 개발기간을 수 개월 단축하기 위해 알테라의 Stratix® II GX에 기반한 개발 키트와 3Gbps 시리얼 디지털 인터페이스(SDI) I인 MegaCore® 기능을 채택했다고 발표했다.

- 16bit 자동차용 마이크로 컨트롤러 판매량 연간 1억개 돌파자동차용 반도체 시장의 리더인 프리스케일 세미컨덕터 (www.freescale.com)는 S12 16bit 자동차용 마이크로 컨트롤러(MCU) 판매량이 최근 연간 1억개 이상 돌파했다고 발표했다. 프리스케일은 100만 분의 1이라는 극히 낮은 불량률을 유지하면서 시장 리더로서 괄목할 만한 실적을 달성했으며, S12 제품군의 판매는 2007년에 들어서면서 급속도로 증가하고 있다.

- IDT DDR3 메모리 모듈 지원하는 고성능 레지스터 발표핵심 반도체 솔루션 선두기업 IDT(www.idt.com 한국지사장 이상엽)는 DDR3 RDIMM(Registered Dual In-line Memory Module)을 지원하는 업계 최고 속도의 JEDEC 호환형 통합 레지스터 및 위상 동기 루프(PLL: Phase-Locked Loop)를 선보였다.

Ceva, TinyML에 최적화된 새로운 NPU로 스마트 엣지 IP 리더십 강화

Ceva, TinyML에 최적화된 새로운 NPU로 스마트 엣지 IP 리더십 강화 엔비디아, 물리 AI 성능 강화한 옴니버스 마이크로서비스 발표

엔비디아, 물리 AI 성능 강화한 옴니버스 마이크로서비스 발표 델 테크놀로지스, 국내 첫 ‘AI PC 팝업 체험존’ 운영

델 테크놀로지스, 국내 첫 ‘AI PC 팝업 체험존’ 운영 마우저, 보안이 강화된 연결성을 제공하는 마이크로칩의 32비트 마이크로컨트롤러 공급

마우저, 보안이 강화된 연결성을 제공하는 마이크로칩의 32비트 마이크로컨트롤러 공급 로데슈바르즈, 3GPP 미션 크리티컬 서비스에 대한 단말 적합성 평가 성공적으로 완료

로데슈바르즈, 3GPP 미션 크리티컬 서비스에 대한 단말 적합성 평가 성공적으로 완료

- 헥사곤, 국제표준 안전보건경영시스템 인증 ISO 45001:2018 취득

- 슈나이더 일렉트릭, HMS 네트웍스로부터 1천만 번째 Anybus 모듈상 수상

- ASML 코리아, WISET과 함께 하는 ‘글로벌 멘토링’ 성료

- 지멘스, 올림피아 익스프레스 커피 머신 설계 및 생산 현대화 지원

- 어플라이드 머티어리얼즈, ‘넷제로 2040 플레이북’ 진척 상황 공유

- 바이코, AID 2024에서 48V 존 아키텍처를 위한 혁신적인 모듈형 솔루션 발표 예정

그래픽 / 영상

많이 본 뉴스

2024년 1분기 전세계 실리콘 웨이퍼 출하량 5% 감소

2024년 1분기 전세계 실리콘 웨이퍼 출하량 5% 감소 한국레노버, AI 지원 모바일 워크스테이션 신제품 5종 출시

한국레노버, AI 지원 모바일 워크스테이션 신제품 5종 출시 웨스턴디지털, 세계 최대 6TB 용량의 2.5인치 포터블 HDD 공개

웨스턴디지털, 세계 최대 6TB 용량의 2.5인치 포터블 HDD 공개 키사이트, RFIC 칩 설계자를 위한 차세대 무선 주파수 회로 시뮬레이터 출시

키사이트, RFIC 칩 설계자를 위한 차세대 무선 주파수 회로 시뮬레이터 출시 CGD, 최고 수준의 효율을 제공하는 새로운 ICeGaN GaN 전력 IC

CGD, 최고 수준의 효율을 제공하는 새로운 ICeGaN GaN 전력 IC Ewon Netbiter EC360W, 개선된 Argos 클라우드 인터페이스와 새로운 모바일 앱 지원

Ewon Netbiter EC360W, 개선된 Argos 클라우드 인터페이스와 새로운 모바일 앱 지원 블루투스 SIG, 오라캐스트 브로드캐스트의 가능성 제시

블루투스 SIG, 오라캐스트 브로드캐스트의 가능성 제시 사피온, 텔레칩스에 AI 반도체 아키텍처 기반의 차량용 NPU IP 공급

사피온, 텔레칩스에 AI 반도체 아키텍처 기반의 차량용 NPU IP 공급 지멘스, 3D IC 설계, 검증 및 제조를 위한 통합 콕핏 솔루션 출시

지멘스, 3D IC 설계, 검증 및 제조를 위한 통합 콕핏 솔루션 출시 헥사곤 ‘APK 파트너 커넥트 2024’ 개최, 아시아 전역에서 파트너사 참가

헥사곤 ‘APK 파트너 커넥트 2024’ 개최, 아시아 전역에서 파트너사 참가

자동차 애플리케이션을 위한 안전한 블루투스 LE 연결

자동차 애플리케이션을 위한 안전한 블루투스 LE 연결 헤드셋 매출의 향방, 하락세는 지속할 것인가?

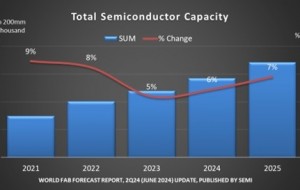

헤드셋 매출의 향방, 하락세는 지속할 것인가? 한국 반도체 생산능력, 올해 첫 5백만장 넘어선다

한국 반도체 생산능력, 올해 첫 5백만장 넘어선다