실리콘 기반 network-on-chip (NoC) 상호 연결 IP 솔루션의 유일한 공급업체인 아테리스(Arteris; www.arteris.com; 지사장 연명흠)가 시스템 온칩(SoC)의 물리적 설계를 가속화시키는 ArterisFlexNoC Physical interconnect IP를 출시했다.

ArterisNoC상호 연결 IP기술은 와이어를 적게 사용하면서도 거의 모든 상호 연결 지점에서 정교한 파이프라인 레지스터 배치를 가능하게 하며 분산 IP 배치를 허용하는 레이아웃 친화적인 솔루션이다. 이 기술은 오랫동안 세계 최고의 반도체 설계 팀에게 배선 정체를 최소화시키고 실리콘 면적, 비용 및 전력 소비를 줄여주는 혜택을 제공해왔다.

FlexNoC Physical interconnect IP는 사용자가 정의한 Floor plan을 임포트한 뒤 타이밍 종료 제약 조건에 부합하도록 자동으로 파이프라인을 구성한다. FlexNoC interconnect IP 인스턴스를 SoC의 나머지 부분과 별개로 라우팅되도록 물리적 차원에서 분리함으로써 결과 품질(QoR; Quality of Result)과 생산성을 증대시킨다.

FlexNoC Physical IP의 이점은 다음과 같다.

1. 과도한 P&R 반복을 억제 혹은 해소 – SoC 설계자들은 긴 경로의 타이밍 종료 오류를 해결하기 위해 비용이 많이 소요되는 P&R 실행을 여러 번 반복해야 하는 경우가 많이 있다. 그러나 완전히 SoC P&R을 하기에 앞서 조기에NoC interconnect IP를 최적화시키면 레이아웃 과정에서 타이밍 종료 문제가 발생할 가능성이 줄어든다.

2. 자동 파이프라인 구성을 통한 타이밍 종료 시행 착오 배제 – 칩 팀은 프론트엔드 설계 단계에서 실제 상호 연결 IP를 분석하고 자동으로 파이프라인 단계를 구성함으로써 설계상 타이밍을 종료시킬 netlist를 백엔드 팀에게 인계한다.

3. 결과 품질 (QoR) 최적화 – SoC팀은 백엔드에서의 타이밍 문제를 피하기 위해 프론트엔드 단계에서 칩을 과잉 설계하는 경우가 많다. FlexNoC Physical IP는 백엔드에서 타이밍 문제가 발생할 프론트엔드 단계를 지능적으로 추정, 예측하므로 설계 팀은 최소한의 파이프라인 단계를 실행하여 원하는 주기를 달성하면서도 지연 현상과 전력 소비를 최소화시킬 수 있다.

4. FlexNoC interconnect physical IP를 SoC의 나머지 부분으로부터 분리 – FlexNoC Physical은 아키텍처 차원과 같은 방식으로 물리적 차원에서 interconnect IP를 분리하는 기능을 제공한다. 이로써 사용자는 상호 연결 평면도 아웃라인을 생성해서 상호 연결부분들을 독립적으로 배치, 라우팅하는 별도의 IP로 처리할 수 있다. 이러한 분리를 통해 레이아웃 팀의 작업이 간소화된다.

FlexNoC Physical 솔루션은 SoC 상호 연결과 관련한 아키텍처 지식을 십분 활용하여 타이밍 종료를 가속화시킨다. 그뿐 나이라 적은 slack을 활용해 타이밍을 충족시키고 SoC 실리콘 면적을 추가로 감소시키면서도 성능을 향상시키므로 결과 품질(QoR)을 향상시킨다.

이러한 자동화를 구현하려면 FlexNoC Physical은 프로세스 기술 정보와 함께 평면도(LEF / DEF 포맷)를 임포트해야 한다. 이 레이아웃과 프로세스 정보를 활용하여 레이아웃에서 최적의 FlexNoC Physical fabric IP 구성 요소들을 찾아 면적과 지연을 최소화하는 한편 어느 지점에서 파이프라인 단계가 활용될지를 결정하게 된다.

FlexNoC Physical은 추가적인 파이프라인 단계와 함께 새로운 RTL 인스턴스를 생성하는 동시에 배치 정보를 물리적 인식 합성 툴과 배치 및 라우트 툴로 익스포트한다

아테리스의 CEO인 찰스 자낙(K. Charles Janac)은 “FlexNoC Physical을 활용하면 다음과 같은 두 가지의 귀중한 혜택을 갖게 된다. 즉, SoC설계자는 설계 주기 초반에 토폴로지의 물리적 의의를 가시화할 수 있으며 RTL 실행 팀이 자동으로 타이밍 종료를 위한 파이프라인을 추가함으로써 복잡한 SoC 개발 주기 시간을 단축하도록 도움을 주게 된다”고 설명했다.

자낙 CEO는 또한 “당사는 고객의 레이아웃 팀에게 보다 나은 스타팅 포인트 데이터를 제공함으로써 고객이 배치 및 라우트 주기를 단축하도록 지원한다”고 덧붙였다.

시장조사 기관인 린리 그룹의 마이크 데믈러(Mike Demler) 선임 애널리스트는“Arteris는 SoC 설계 흐름의 초반에 꼭 필요한 기술을 제공함으로써 중요한 백엔드 문제들을 쉽게 해결하도록 해준다”며 “FlexNoC Physical IP는 레이아웃 단계에서 겪는 타이밍 문제를 대폭 줄여주고 P&R 반복과 엔지니어링 변경 순서(ECO; Engineering change orders)를 단축시킴으로써 결과적으로 비용과 스케줄 시간을 절감하는 잠재력을 갖췄다"고 언급했다.

시놉시스의 비잔 키아니(Bijan Kiani) Design Group마케팅 부사장은 “ArterisFlexNoC Physical은 타이밍 종료 정보를 개선하고 보다 정확한 RTL 데이터를 제공하는 Design Compiler Graphical 및 IC Compiler II와 같은 당사의 툴을 제공함으로써 레이아웃 생산성을 향상시킬 잠재력을 제공한다”며 "당사는 양측 고객들과 협력하여 이러한 장점을 지속적으로 검증할 것이다”라고 설명했다.

구매 정보

ArterisFlexNoC Physical은 당장 구매가 가능하다.

관련 링크 : http://www.arteris.com

저작권©올포칩 미디어. 무단전재 및 재배포를 금지합니다.

- 플리어시스템, 2015 국제전기전력전시회 참가열화상 카메라 전문기업 플리어 시스템(FLIR Systems)이 2015 국제전기전력전시회(Global Electric Power Tech 2015)에 참가하여 자사의 최신 산업용 제품을 선보인다.

- 멘토 그래픽스의 MicReD 산업용 파워 테스터, 부품 파워 사이클링 속도 4배 높이고 열 테스트 성능도 향상반도체 설계 자동화(EDA) 기술 및 시장을 선도하는 한국 멘토그래픽스(www.mentorkr.com, 지사장 양영인)는 오늘 차세대 MicReD® Industrial Power Tester 1500A 제품을 발표했다. 이 제품은 전자 부품의 파워 사이클링 및 열 테스트를 최대 12개의 디바이스에 대해 동시에 수행할 수 있다.

- HDBaseT 얼라이언스 최초로 KOBA 참여HDBaseT 인터페이스 기술을 권장하고 활성화하는 표준 단체인 HDBaseT 얼라이언스(www.hdbaset.org)가 오는 5월 19일부터 22일까지 사흘간 서울 코엑스에서 개최되는 국제 방송, 음향 조명기기 전시회(이하 KOBA 2015)에 참가한다.

- MOXA, 열차와 지상간 통신을 위한 “올인원” 선로변 액세스 포인트 출시MOXA는 2개 액세스 포인트, 관리식(managed) 광 스위치, 넓은 입력전압 AC/DC 전원 공급 장치를 통합하고 신뢰할 수 있는 열차와 지상간 통신을 가능하게 하는 “올인원” 무선 유닛인 TAP-6226을 출시한다고 밝혔다.

- TI, MaxCharge™ 기술로 배터리 충전 시간 60%까지 단축TI (대표이사 켄트 전)는 업계 최초의 완전 통합형 5A 단일 셀 리튬이온(Li-ion) 배터리 충전 IC를 출시했다. 이 신제품은 보다 빠르게 낮은 온도에서 충전할 수 있는 고유의 MaxCharge 기술을 적용해 충전 시간을 기존 배터리 충전 IC 대비 최대 60%까지 단축시켰다

- 뛰어난 민감도와 저전력 특성을 갖춘 마이크렐의 새로운 RF 리시버 출시마이크렐 코리아(대표이사 오영준, www.micrel.com), 고성능 리니어 및 전력 솔루션을 비롯해 LAN, 타이밍, 통신 솔루션 분야의 업계 선도주자인 마이크렐은 400MHz ~ 450MHz의 저전력 수퍼 헤테로다인(Super-Heterodyne), 이미지 제거 및 OOK/ASK 리시버 제품군, MICRF229 및 MICRF230을 출시했다.

- 리니어, 80dB SFDR 실현하는 16비트, 2.7Gsps DAC 출시리니어 테크놀로지 코리아(대표 홍사곽)는 하이엔드 광대역 유선, 무선 통신 및 레이더 애플리케이션에 최적화된 16비트 2.7Gsps DAC(digital-to-analog converter)(제품명: LTC2000A)를 출시한다고 밝혔다.

- 인피니언, 전기기계식 릴레이 대체하는 HITFET™+ 스위치 제품군 출시인피니언 테크놀로지스(코리아 대표이사 이승수)는 릴레이를 좀더 견고한 반도체 솔루션으로 전환하는 경향에 대응하기 위해 HITFET™+ 보호기능 로우사이드 스위치 제품군을 출시했다.

- 프리스케일, 새로운 에어페스트(Airfast) 제품으로 항공 전자 기기 시장을 위한 RF 전력 포트폴리오 확장프리스케일 반도체(www.freescale.co.kr 한국 대표이사 황연호)는 항공 전자 기기 관련 고객에게 추세에 맞는 대응을 지원하기 위해 탁월한 시스템 기능 통합과 광대역 고출력 성능을 갖춘 두 개의 RF 전력 트랜지스터를 통해 L-밴드 포트폴리오를 확장했다.

- ARM, 어플라이드마이크로•넷진과 새로운 NFV 플랫폼 발표저전력 고효율 프로세서 기술 선도기업 ARM은 어플라이드마이크로(AppliedMicro) 및 서버 소프트웨어 개발업체인 넷진(Netzyn)과 함께 NFV(Network Functions Virtualization, 네트워크 기능 가상화)를 활용한 새로운 가상 셋톱박스(vSTB)의 레퍼런스 플랫폼을 발표했다.

- 램리서치 코리아, 제 5회 대학(원)생 논문공모전 실시반도체 장비 업계를 선도하고 있는 램리서치 코리아는 오는 5월 11일부터 10월 31일까지 '제 5회 대학(원)생 논문공모전'을 실시한다고 밝혔다.

- TI, 고속 데이터 처리 제품을 최대 3배 빠르게 개발할 수 있는 디지털 프론트 엔드 및 JESD204B를 통합한 고집적 SoC 출시TI(대표이사 켄트 전)는 고속 데이터 생성 및 처리 제품에 대한 요구 사항을 반영한 신제품을 출시했다.

- 온세미컨덕터와 에프터마스터 오디오 랩, 혁신적인 오디오 클립 출시온세미컨덕터 (www.onsemi.com)는 스튜디오 원 미디어의 자회사이자 캘리포니아 할리우드에 본사를 둔 업계 최고의 오디오 기술회사인 AferMaster와 함께 BelaSigna 300® AM를 출시했다. AfterMaster 기술을 탑재한 새로운 BelaSigna 300 AM 디지털 신호 처리 칩(DSP)은 어떤 소비자용 기기에서도 청취 경험을 향상시켜주는 획기적인 오디오 솔루션이다,

- NXP, 퀄컴과 NFC와 임베디드 보안칩(eSE) 도입 가속화 위해 협력NXP 반도체는 퀄컴 테크놀로지(Qualcomm Technologies, Inc.)가 업계 최고의 NXP 근거리무선통신(NFC)과 임베디드 보안칩(eSE) 솔루션을 퀄컴 스냅드래곤(Qualcomm® Snapdragon™) 800, 600, 400, 200 프로세서 기반 플랫폼 전체에 통합하기로 했다고 발표했다.

Ceva, TinyML에 최적화된 새로운 NPU로 스마트 엣지 IP 리더십 강화

Ceva, TinyML에 최적화된 새로운 NPU로 스마트 엣지 IP 리더십 강화 엔비디아, 물리 AI 성능 강화한 옴니버스 마이크로서비스 발표

엔비디아, 물리 AI 성능 강화한 옴니버스 마이크로서비스 발표 델 테크놀로지스, 국내 첫 ‘AI PC 팝업 체험존’ 운영

델 테크놀로지스, 국내 첫 ‘AI PC 팝업 체험존’ 운영 마우저, 보안이 강화된 연결성을 제공하는 마이크로칩의 32비트 마이크로컨트롤러 공급

마우저, 보안이 강화된 연결성을 제공하는 마이크로칩의 32비트 마이크로컨트롤러 공급 로데슈바르즈, 3GPP 미션 크리티컬 서비스에 대한 단말 적합성 평가 성공적으로 완료

로데슈바르즈, 3GPP 미션 크리티컬 서비스에 대한 단말 적합성 평가 성공적으로 완료

- 헥사곤, 국제표준 안전보건경영시스템 인증 ISO 45001:2018 취득

- 슈나이더 일렉트릭, HMS 네트웍스로부터 1천만 번째 Anybus 모듈상 수상

- ASML 코리아, WISET과 함께 하는 ‘글로벌 멘토링’ 성료

- 지멘스, 올림피아 익스프레스 커피 머신 설계 및 생산 현대화 지원

- 어플라이드 머티어리얼즈, ‘넷제로 2040 플레이북’ 진척 상황 공유

- 바이코, AID 2024에서 48V 존 아키텍처를 위한 혁신적인 모듈형 솔루션 발표 예정

그래픽 / 영상

많이 본 뉴스

에이디링크, ASD+ 엔터프라이즈 시리즈 SSD 출시 발표

에이디링크, ASD+ 엔터프라이즈 시리즈 SSD 출시 발표 사피온 AI반도체 ‘X330’, 슈퍼마이크로 서버 적격성 평가 완료

사피온 AI반도체 ‘X330’, 슈퍼마이크로 서버 적격성 평가 완료 마우저, IoT 애플리케이션을 유블럭스의 새로운 익스플로러 키트 공급

마우저, IoT 애플리케이션을 유블럭스의 새로운 익스플로러 키트 공급 엘리먼트14 커뮤니티, ‘인공 지능의 눈(Eye on Intelligence)’ 설계 공모전 시작

엘리먼트14 커뮤니티, ‘인공 지능의 눈(Eye on Intelligence)’ 설계 공모전 시작 에이디링크, 차세대 철도 솔루션 공개: AVA-7200, AVA-1000 및 승객 정보 디스플레이 시스템 (PIDS)

에이디링크, 차세대 철도 솔루션 공개: AVA-7200, AVA-1000 및 승객 정보 디스플레이 시스템 (PIDS) 하이크비전, 성능과 편의성 개선한 5세대 LED 캐비닛 출시

하이크비전, 성능과 편의성 개선한 5세대 LED 캐비닛 출시 듀어와 로데슈바르즈, EOL 및 PTI를 위한 ADAS/AD 테스트 지원 솔루션 개발

듀어와 로데슈바르즈, EOL 및 PTI를 위한 ADAS/AD 테스트 지원 솔루션 개발 Ewon Netbiter EC360W, 개선된 Argos 클라우드 인터페이스와 새로운 모바일 앱 지원

Ewon Netbiter EC360W, 개선된 Argos 클라우드 인터페이스와 새로운 모바일 앱 지원 에이디링크, 수상 경력에 빛나는 ARM 기반 패널 PC 출시

에이디링크, 수상 경력에 빛나는 ARM 기반 패널 PC 출시 헥사곤 ‘APK 파트너 커넥트 2024’ 개최, 아시아 전역에서 파트너사 참가

헥사곤 ‘APK 파트너 커넥트 2024’ 개최, 아시아 전역에서 파트너사 참가

자동차 애플리케이션을 위한 안전한 블루투스 LE 연결

자동차 애플리케이션을 위한 안전한 블루투스 LE 연결 헤드셋 매출의 향방, 하락세는 지속할 것인가?

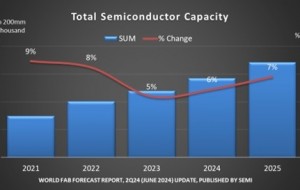

헤드셋 매출의 향방, 하락세는 지속할 것인가? 한국 반도체 생산능력, 올해 첫 5백만장 넘어선다

한국 반도체 생산능력, 올해 첫 5백만장 넘어선다