두 회사는 지난 1년 여 동안 자일링스의 초고밀도 설계로 구현된 65 나노미터 버텍스-5 FPGA의 결과 품질과 생산성 극대화를 위한 솔루션을 정의하고 개발하는데 협력해왔다. 양사 태스크포스의 첫 번째 성과는 스마트컴파일 기술(SmartCompile™ Technology)의 개발로, 지난 2006년 5월 발표한 바 있다. 스마트컴파일 기술은 인크리멘탈 설계 방법(an incremental design flow)으로 설계와 로직을 보전하면서도 런타임을 6배 이상 개선하였으며, 스마트컴파일의 RTL to P&R 방법(This RTL to place-and route flow)은 인크리멘탈 변화를 지원하기 때문에 설계를 조금 변경했을 때 전체 설계를 재실행할 필요가 없다.

양 사는 태스크포스팀 운영 초기 단계에서 주로 FPGA 설계에 인크리멘탈 변화를 주었을 때, 그 결과와 런타임을 전반적으로 개선하고, 결과의 안정성을 향상시키는 것에 주력한 결과 만족할만한 성과를 얻어냈다. 태스크포스 팀은 2단계에서65나노미터 및 그 이하에서 영역 축소와 소비 전력 감소에 초점을 맞추는 공정에 주력할 것이며, 그 목표는 다중 설계 반복 공정을 하루 안에 마칠 수 있는 능력과 함께 초고밀도 설계를 위한 푸시-버튼 수준의 결과를 설계자에게 제공하는 것이다.

초 고밀도 설계에서 디자이너에게 푸시 버튼에 근접한 결과를 하루에도 몇 번씩 반복 수행할 수 있는 능력과 함께 제공하는 것을 목표로 한다. 또한, 태스크 포스팀은 초 고성능 FPGA에 기반을 둔 다양한 어플리케이션을 고려하여, 독특한 설계에 최적화된 복잡한 설계와 툴을 제공할 것이다.

신플리시티의 켄 맥얼베인(Ken McElvain) CTO는 “우리는 인크리멘털 설계 지원을 향상시킨 태스크포스 팀의 첫 번째 성과에 만족하며, 앞으로 태스크포스 팀의 활동 영역이 FPGA 기반의 설계와 검증을 위한 기회 요소- 고객사들이 가장 걱정하고 있는 영역 문제와 전력 소모까지-들까지 포함하는 더 넓은 영역으로 확장되기를 기대하고 있다”고 태스크포스 팀의 2단계 활동에 대해 설명했다.

자일링스의 소프트웨어 담당 부사장인 브루스 탤리(Bruce Talley)는 “우리는 앞으로도 자일링스가 추진하는 설계 협업의 2단계 사업과 관련해 신플리시티와 더욱 긴밀한 협력관계를 유지하기 바란다. 신플리시티와 함께 한 태스크포스 팀은 각 사의 기술과 공학적인 역량을 통해 단일화된 솔루션을 만들기 위한 여러 난제들을 잘 해결해 왔다. 양사는 앞으로도 상호 고객에게 자일링스 65나노미터 FPGA 기반의 적은 공간과 낮은 전력을 사용하는 개선된 설계 환경을 지원하는 솔루션을 제공하는데 지속적으로 협력해 나갈 것이다”라고 협력의 의의를 설명했다.

저작권©올포칩 미디어. 무단전재 및 재배포를 금지합니다.

- 자일링스 휴대용 컨수머 기기 시장에서 경이적인 매출 성장 기록세계적인 프로그래머블 로직 솔루션 공급업체인 자일링스는 PDA, 휴대폰, MP3 플레이어 등과 같은 휴대용 컨수머 애플리케이션에서 최근 CPLD 매출액이 두 자리 수의 성장률을 기록했다고 발표했다.

- 프리스케일 반도체 코리아 신임 최 충원 사장 임명프리스케일 반도체 코리아는 신임 한국사장에 최 충원사장을 임명했다고 발표했다.

- CSR 블루투스 분야의 신기술을 포함한 제품 로드맵 공개CSR은 업계 최초의 첫 ULP 블루투스(초저전력 블루투스) 칩셋을 선보일 계획이며, 2008년에 생산 예정인 이 ULP 블루투스 칩셋은 시장 선도적인 자사의 몇몇 고객사들을 대상으로 샘플링을 시작할 예정이라고 밝혔다.

- 마이크로칩 ‘온라인 조명 애플리케이션 디자인 센터’ 개설세계적인 마이크로컨트롤러 및 아날로그 반도체 전문업체인 마이크로칩 테크놀로지는 ‘온라인 조명 애플리케이션 디자인 센터’(www.micorchip.com/lighting) 웹사이트를 오픈했다.

- STR9 ARM966E 코어 기반 MCU용 초저가형 개발 킷트세계적인 마이크로컨트롤러 공급 업체인 ST마이크로일렉트로닉스는 자사의 가장 강력한 STR91x 32-비트 마이크로컨트롤러 제품군을 위해 통합형의 매우 저가형인 평가 및 개발 킷트를 출시했다.

- 아바고 새로운 초소형 고체 릴레이로 높은 시스템 처리율 보장아바고테크놀로지스코리아(주)(대표: 전성민) 광절연 제품의 확장된 고체 릴레이(MOSFET) 제품군을 발표했다. 아바고는 통신, 산업용 및 소비자 어플리케이션을 위한 아날로그 인터페이스 부품을 공급하는 글로벌 공급업체이다.

- 신플리시티 하디 일렉트로닉스AB 인수세계적인 반도체 디자인 및 검증 소프트웨어 공급업체인 신플리시티(Synplicity)는 오늘 규격형(off-the-shelf) 프로토타이핑 보드 분야의 선도기업인 ‘하디 일렉트로닉스 AB(HARDI Electronics AB)’사를 총 2천420만 달러에 인수한다고 발표했다. 신플리시티는 최근 하디사와 이 회사의 잔여 주식 전체에 대한 인수에 최종합의 한 바 있다.

- 싸이프레스 고성능 고집적의 레이저 네비게이션 센서 출시싸이프레스 코리아 (지사장 손병세 www.cypress.com)는 자사의 오베이션ONS (OvationONS) 레이저 네비게이션 센서 제품군의 일환으로 높은 정밀도를 가진 고성능 레이저 네비게이션 센서인 CYONS1001G를 발표했다.

- RF/IF 증폭기 추가로 완벽한 RF 포트폴리오세계적인 신호 처리 애플리케이션용 고성능 반도체 부문 선두 기업인 아나로그디바이스(www.analog.com 한국 지사장: 전고영)는 전체 RF 신호 체인을 아우르는 12가지 신규 RF(무선 주파수) 증폭기를 발표, RF 솔루션의 포트폴리오를 확장했다고 밝혔다.

- 삼성전자고용량 메모리 카드를 탑재한 복합칩 개발삼성전자가 휴대폰용 적층칩 (MCP:Multi Chip Package)에 고용량 메모리 카드를 탑재한 복합칩인 moviMCP (모비MCP)를 세계 최초로 개발, 주요 휴대폰 업체를 대상으로 공급하기 시작했다.

- 내셔널 세미컨덕터 스테레오 스피커 드라이버 출시내셔널 세미컨덕터 코리아는 다양한 3V 휴대용 기기에서 세라믹 스피커를 구동할 수 있는 업계 최고 출력의 단일 칩 Boomer® 오디오 파워 앰프를 출시한다고 발표했다.

- CEVA 32비트 프로세싱 DSP 아키텍쳐 출시세바는 3세대 DSP 아키텍쳐 기반 DSP코어의 TeakLite 제품군인 CEVA-TeakLite-III™을 출시했다.

- 프리스케일 무선 제어용 저전력 RF 송신/수신 디바이스 발표프리스케일 세미컨덕터(www.freescale.com) 는 자사 RF 제품군의 최신 제품으로 저전력 무선 연결 기능을 갖춘 디바이스를 발표했다. MC33696 PLL 튜닝 UHF 송신기와 MC33596 저전압 수신기는 개발회사들이 기존 RF 솔루션을 능률화하고 자사 제품에 보다 편리하게 무선 제어 기능을 추가할 수 있도록 설계된 액세스 및 원격 제어 디바이스이다.

- 탠드버그 고해상 HD 영상 회의 시장의 선두주자세계적인 영상 커뮤니케이션 솔루션 공급 업체인 탠드버그가 2006년 6월 처음으로 HD제품을 선보인 이후 Full HD(720p@ 30fps)를 구현하는 새로운 소프트웨어를 발표하였다. 이번에 출시된 소프트웨어를 통해 초 당 30 프레임의 고해상도의 HD 기술을 엔드 투 엔드(end-to-end) 솔루션으로 고객에게 제공하며, 뿐만 아니라 단 몇 분 이내에 다운 받아 설치할 수 있는 편의성을 갖고 있어 기업들의 관심이 집중되고 있다.

오직 나 만을 위한 ‘맞춤형’ 제품을 위한 추천 아이템 3종

오직 나 만을 위한 ‘맞춤형’ 제품을 위한 추천 아이템 3종 KT, ‘퀀텀 코리아 2024’에서 순수 국내 기술로 개발한 양자암호통신기술 선보인다

KT, ‘퀀텀 코리아 2024’에서 순수 국내 기술로 개발한 양자암호통신기술 선보인다 코보, 첨단 레이더 애플리케이션을 위한 RF 멀티칩 모듈 출시

코보, 첨단 레이더 애플리케이션을 위한 RF 멀티칩 모듈 출시 맨디언트, 2024 M-트렌드 보고서- 공격 지속시간 사상 최저치 기록

맨디언트, 2024 M-트렌드 보고서- 공격 지속시간 사상 최저치 기록 유블럭스, 새로운 초소형 LTE Cat 1bis 셀룰러 모듈로 글로벌 연결성 강화

유블럭스, 새로운 초소형 LTE Cat 1bis 셀룰러 모듈로 글로벌 연결성 강화

- ST, 대규모 IoT 기기의 혁신적 관리 위한 새로운 표준 지원하는 임베디드 SIM 출시

- 바이코, 전력전자학술대회에서 전력 설계를 혁신하는 고밀도 전력모듈 발표

- 헥사곤 ‘스마트 스캔 VR800 3D’ 스캐너, 레드닷 디자인 어워드 제품 디자인 부문 수상

- 포티넷, ‘2024 글로벌 OT 운영기술 및 사이버 보안 현황 보고서' 발표

- 어플라이드 머티어리얼즈 코리아, 초록우산어린이재단과 지역사회 교육 지원

- KT, 100 기가 전국 전송망 구축으로 전용회선 및 유무선 안정성 향상

그래픽 / 영상

많이 본 뉴스

마우저, IoT 애플리케이션을 위한 코보의 다중 표준 스마트 홈 통신 컨트롤러 QPG6105 공급

마우저, IoT 애플리케이션을 위한 코보의 다중 표준 스마트 홈 통신 컨트롤러 QPG6105 공급 Synology, 대만 컴퓨텍스 2024 기간 고급 데이터 보호, 데이터 관리 및 영상 보안 감시 솔루션 선봬

Synology, 대만 컴퓨텍스 2024 기간 고급 데이터 보호, 데이터 관리 및 영상 보안 감시 솔루션 선봬 헥사곤-영남대, 미래차 융합 인재 양성 MOU 체결

헥사곤-영남대, 미래차 융합 인재 양성 MOU 체결 코보(Qorvo), 업계 최고 이득의 5G mMIMO용 프리 드라이버 출시

코보(Qorvo), 업계 최고 이득의 5G mMIMO용 프리 드라이버 출시 엔비디아 젠슨 황, AI 기반 전력망에 대한 긍정적 전망 제시

엔비디아 젠슨 황, AI 기반 전력망에 대한 긍정적 전망 제시 엔비디아, 생성형 AI 통해 HPC 연구 가속화

엔비디아, 생성형 AI 통해 HPC 연구 가속화 싸이타임, AI 데이터센터를 위한 통합 클럭 칩으로 정밀 타이밍 기술 발전

싸이타임, AI 데이터센터를 위한 통합 클럭 칩으로 정밀 타이밍 기술 발전 슈퍼마이크로, AI 시대를 위한 혁신 서버 AI 슈퍼클러스터 선보여

슈퍼마이크로, AI 시대를 위한 혁신 서버 AI 슈퍼클러스터 선보여 모터 제어 애플리케이션에 GaN의 이점을 제공하는 CGD

모터 제어 애플리케이션에 GaN의 이점을 제공하는 CGD KT, 마이크로소프트와 대한민국 AI·클라우드 혁신 이끈다

KT, 마이크로소프트와 대한민국 AI·클라우드 혁신 이끈다

헤드셋 매출의 향방, 하락세는 지속할 것인가?

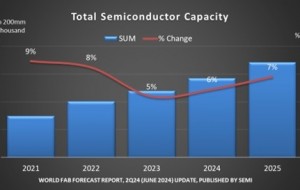

헤드셋 매출의 향방, 하락세는 지속할 것인가? 한국 반도체 생산능력, 올해 첫 5백만장 넘어선다

한국 반도체 생산능력, 올해 첫 5백만장 넘어선다 실리콘 카바이드로 배터리 에너지 저장 시스템 향상

실리콘 카바이드로 배터리 에너지 저장 시스템 향상