적응형 컴퓨팅 가속화 플랫폼으로 데이터 센터 시장 공략

글/ 진선옥 기자(jadejin@all4chip.com)

프로그래머블 디바이스 시장을 선도하는 자일링스가 FPGA를 넘어서는 새로운 차원의 솔루션으로 미래의 시스템 플랫폼의 역사를 다시 쓰고 있다. 자일링스가 새롭게 선보일 ACAP(Adaptive Compute Acceleration Platform)은 ‘FPGA가 발명된 이후 산업계와 엔지니어링 성과를 뒤엎을 가장 혁신적인 기술’이라는 평가를 받고 있다.

자일링스 코리아의 안흥식 지사장은 “데이터의 폭발적 증가, AI의 등장, 무어의 법칙을 넘어선 컴퓨팅 환경은 기존의 범주를 넘어서는 새로운 차원의 플랫폼을 요구하고 있다.”고 말하고, “자일링스는 이러한 시장의 요구에 대응할 수 있는 미래 지향적 솔루션으로 적응형 컴퓨팅 가속화 플랫폼을 개발했으며, 이는 기존의 FPGA나, CPU 또는 GPU를 뛰어넘는 획기적인 엔지니어링 성과로 기록될 것이다.”고 밝혔다.

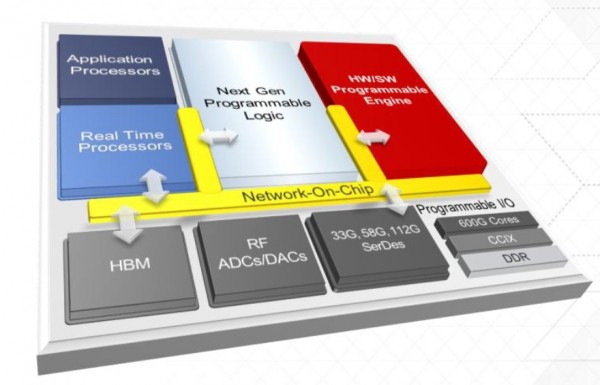

ACAP은 다양한 애플리케이션과 작업량의 요구에 적응할 수 있도록 하드웨어 레벨에서 변경이 가능한 멀티코어 기반의 이기종 컴퓨팅 플랫폼이다. 동작 중에 동적으로 수행되는 ACAP의 적응성은 CPU 또는 GPU를 뛰어넘는 새로운 차원의 와트 당 성능을 제공할 것으로 기대되고 있다.

안흥식 사장은 “자일링스는 이 ACAP 프로젝트 진행을 위해 지난 4년 동안 1,500명이 넘는 하드웨어 및 소프트웨어 엔지니어를 투입해 새로운 아키텍처를 개발하는데 전념해 왔으며, 10억 달러 이상을 R&D에 투자했다.”고 말하고, “이 적응형 플랫폼은 자일링스를 데이터 센터 애플리케이션의 핵심 경쟁주자로 세우는 주요 동력이 될 것”이라고 밝혔다.

최초의 ACAP 제품군인 코드네임 ‘에베레스트’는 TSMC 7나노미터 공정 기술로 개발되며, 올해 말 개발이 완료될 예정이다. 에베레스트는 최신 16나노미터 버텍스 VU9P FPGA와 비교해 DNN(Deep Neural Networks) 애플리케이션에서 20배 이상의 성능 개선을 달성할 것으로 예상된다. 에베레스트 기반 5G 원격 무선 헤드는 최신 16나노미터 기반 무선통신 대비 4배의 대역폭을 갖게 된다.

ACAP은 분산형 메모리 및 하드웨어 프로그래머블 DSP 블록, 멀티코어 SoC, 하나 이상의 프로그래머블 소프트웨어, 적응형 하드웨어, 컴퓨팅 엔진, 네트워크 온 칩(NoC)을 통한 모든 연결이 가능한 차세대 FPGA 패브릭을 갖추고 있다. 또한 ACAP은 하드웨어 프로그래머블 메모리 컨트롤러, 향상된 SerDes 기술과 첨단 RF-ADC/DAC를 집적하고 있으며, 디바이스 종류에 따라서 HBM(High Bandwidth Memory)까지 집적화된 고도의 통합된 프로그래머블 I/O 기능을 갖추고 있다.

에베레스트는 2018년에 개발 완료될 예정이며, 2019년에는 고객들에게 출하될 예정이다.

관련 링크 : https://www.xilinx.com/

저작권©올포칩 미디어. 무단전재 및 재배포를 금지합니다.

TI, 산업용 전압 감지 애플리케이션에서 긴 수명을 보장하는 고정밀 강화 절연 증폭기 제품 출시TI는 업계 최고의 정밀도와 동작 전압을 제공하며, 긴 수명의 신뢰성이 뛰어난 새로운 강화 절연 증폭기 제품을 출시한다고 밝혔다. 개발자들은 보다 우수한 비선형성, 낮은 오프셋 및 이득 오차, 높은 온도 안정성을 특징으로 하는 ISO224를 사용함으로써 성능 한계를 극복하고 고정밀 시스템을 설계할 수 있다.

TI, 산업용 전압 감지 애플리케이션에서 긴 수명을 보장하는 고정밀 강화 절연 증폭기 제품 출시TI는 업계 최고의 정밀도와 동작 전압을 제공하며, 긴 수명의 신뢰성이 뛰어난 새로운 강화 절연 증폭기 제품을 출시한다고 밝혔다. 개발자들은 보다 우수한 비선형성, 낮은 오프셋 및 이득 오차, 높은 온도 안정성을 특징으로 하는 ISO224를 사용함으로써 성능 한계를 극복하고 고정밀 시스템을 설계할 수 있다. ASCO, 업스트림 오일 및 가스 가열 장치를 위한 솔레노이드 밸브 기술최근 몇 년 동안 최신 세대의 솔레노이드 밸브 기술이 차단 밸브 시장의 판도를 변화시키고 있다. 이러한 최신 설계를 통해 견고하고 내구성 있는 성능과 안전, 규제준수 등을 모두 제공하면서도 효율성과 생산성을 높일 수 있는 파이프라인 및 탱크 가열 시스템이 공급되고 있다.

ASCO, 업스트림 오일 및 가스 가열 장치를 위한 솔레노이드 밸브 기술최근 몇 년 동안 최신 세대의 솔레노이드 밸브 기술이 차단 밸브 시장의 판도를 변화시키고 있다. 이러한 최신 설계를 통해 견고하고 내구성 있는 성능과 안전, 규제준수 등을 모두 제공하면서도 효율성과 생산성을 높일 수 있는 파이프라인 및 탱크 가열 시스템이 공급되고 있다. 반도체 시장, 2038년에 36.8%의 최고 성장률 기록한다!2017년 이전 6년 동안 3% 미만의 저조한 성장세를 기록했던 반도체 시장의 회복 가능성에 대해 의문을 제기했던 사람들에게 새로운 전망론이 제기됐다.

반도체 시장, 2038년에 36.8%의 최고 성장률 기록한다!2017년 이전 6년 동안 3% 미만의 저조한 성장세를 기록했던 반도체 시장의 회복 가능성에 대해 의문을 제기했던 사람들에게 새로운 전망론이 제기됐다.  산업용 이더넷 시장의 선도주자인 Moxa, 한국 시장에서 빠른 성장세 기록산업용 네트워크 분야에서 30년 이상 전문성을 구축해온 Moxa의 국내 행보가 더욱 가속화되고 있다. Moxa는 에지 커넥티비티에서 산업용 컴퓨팅과 네트워크 인프라 솔루션 등 다양한 제품 라인을 통해 IIoT(Industrial Internet of Things) 시장에서 입지를 강화하고 있다.

산업용 이더넷 시장의 선도주자인 Moxa, 한국 시장에서 빠른 성장세 기록산업용 네트워크 분야에서 30년 이상 전문성을 구축해온 Moxa의 국내 행보가 더욱 가속화되고 있다. Moxa는 에지 커넥티비티에서 산업용 컴퓨팅과 네트워크 인프라 솔루션 등 다양한 제품 라인을 통해 IIoT(Industrial Internet of Things) 시장에서 입지를 강화하고 있다.  텍트로닉스, 13GHz 및 18GHz 모델 출시로 USB 스펙트럼 분석기 포트폴리오 확장텍트로닉스가 각각 13GHz와 18GHz 주파수 범위를 제공하는 RSA513A와 RSA518A를 새롭게 출시하여 배터리 구동식 USB 기반 스펙트럼 분석기 RSA500 제품군을 확장했다.

텍트로닉스, 13GHz 및 18GHz 모델 출시로 USB 스펙트럼 분석기 포트폴리오 확장텍트로닉스가 각각 13GHz와 18GHz 주파수 범위를 제공하는 RSA513A와 RSA518A를 새롭게 출시하여 배터리 구동식 USB 기반 스펙트럼 분석기 RSA500 제품군을 확장했다.  TI, 차량에서 공장까지 밀리미터파 센서로 보다 스마트한 세상 만들어TI는 세계적으로 가장 정확도가 우수한 밀리미터파(mmWave) 단일칩 CMOS 센서를 발표한지 1년 만에, 고집적 초광대역 AWR1642 및 IWR1642 mmWave 센서 제품의 양산을 시 작한다고 밝혔다.

TI, 차량에서 공장까지 밀리미터파 센서로 보다 스마트한 세상 만들어TI는 세계적으로 가장 정확도가 우수한 밀리미터파(mmWave) 단일칩 CMOS 센서를 발표한지 1년 만에, 고집적 초광대역 AWR1642 및 IWR1642 mmWave 센서 제품의 양산을 시 작한다고 밝혔다.  자동차 분야로 확장하는 eGaN® 기술 EPC(Efficient Power Conversion)는 자동차 및 다른 혹독한 환경의 애플리케이션으로 확장이 가능하도록 두 종의 eGaN 디바이스에 대한 AEC Q101 인증을 성공적으로 획득했다고 밝혔다

자동차 분야로 확장하는 eGaN® 기술 EPC(Efficient Power Conversion)는 자동차 및 다른 혹독한 환경의 애플리케이션으로 확장이 가능하도록 두 종의 eGaN 디바이스에 대한 AEC Q101 인증을 성공적으로 획득했다고 밝혔다- ST마이크로일렉트로닉스와 시그폭스, 수십억 개 디바이스의 커넥티비티 향상 위해 협업다양한 전자 애플리케이션에 걸쳐 고객들에게 기여하는 세계적인 반도체 회사인 ST마이크로일렉트로닉스(STMicroelectronics, 이하 ST)와 IoT 서비스 분야의 세계적인 선도 공급업체인 시그폭스(Sigfox)가 다양한 애플리케이션의 커넥티드 디바이스에 대한 지원과 수요 확대를 위해 협약을 체결했다고 밝혔다.

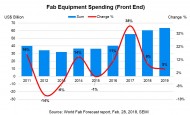

전세계 반도체 팹장비 투자 4연 연속 성장SEMI가 2018년 2월 28일에 발표한 세계 팹 전망 보고서에 따르면, 2019년 반도체 팹 장비 투자는 5% 성장을 하며, 4년 연속 주목할 만한 성장을 보일 것이라 전망했다

전세계 반도체 팹장비 투자 4연 연속 성장SEMI가 2018년 2월 28일에 발표한 세계 팹 전망 보고서에 따르면, 2019년 반도체 팹 장비 투자는 5% 성장을 하며, 4년 연속 주목할 만한 성장을 보일 것이라 전망했다 페라테크, 3D 포스 터치 센서 통합한 최초의 플렉시블 디스플레이 발표3D 포스 센싱(force-sensing) 기술의 세계적 선도기업인 페라테크(Peratech)는 플렉시블 유기 LCD(organic LCD, OLCD)와 함께 통합되는 AM(active-matrix) 3D 포스 터치 센서를 발표했다.

페라테크, 3D 포스 터치 센서 통합한 최초의 플렉시블 디스플레이 발표3D 포스 센싱(force-sensing) 기술의 세계적 선도기업인 페라테크(Peratech)는 플렉시블 유기 LCD(organic LCD, OLCD)와 함께 통합되는 AM(active-matrix) 3D 포스 터치 센서를 발표했다.  TI, GaN 전원 제품군에 업계 최소형의 최고속 GaN 드라이버 추가TI 는 업계를 선도하는 자사의 갈륨 나이트라이드(GaN) 전력 제품 포트폴리오에 새로운 고속 GaN FET 드라이버 제품 2종을 추가한다고 밝혔다. 이들 신제품은 라이다(LIDAR)나 5G RF 포락선 추적과 같이 속도를 중요하게 요구하는 애플리케이션에서 보다 효율적이고 성능이 우수한 설계를 구현할 수 있도록 한다.

TI, GaN 전원 제품군에 업계 최소형의 최고속 GaN 드라이버 추가TI 는 업계를 선도하는 자사의 갈륨 나이트라이드(GaN) 전력 제품 포트폴리오에 새로운 고속 GaN FET 드라이버 제품 2종을 추가한다고 밝혔다. 이들 신제품은 라이다(LIDAR)나 5G RF 포락선 추적과 같이 속도를 중요하게 요구하는 애플리케이션에서 보다 효율적이고 성능이 우수한 설계를 구현할 수 있도록 한다. Arm, 안전한 IoT를 위한 범용 산업 프레임워크 제시영국 반도체 설계자산(IP) 기업인 Arm(www.arm.com)이 위협 모델과 보안 분석(Threat Models and Security Analyses, TMSA) 문서를 공개하고, PSA 사양을 준수하는 최초의 오픈소스 참조 구현 펌웨어인 Trusted Firmware-M을 발표했다.

Arm, 안전한 IoT를 위한 범용 산업 프레임워크 제시영국 반도체 설계자산(IP) 기업인 Arm(www.arm.com)이 위협 모델과 보안 분석(Threat Models and Security Analyses, TMSA) 문서를 공개하고, PSA 사양을 준수하는 최초의 오픈소스 참조 구현 펌웨어인 Trusted Firmware-M을 발표했다.  Arm, 강력한 시각 경험 보편화를 위한 말리 멀티미디어 IP 제품군 발표영국 반도체 설계자산(IP) 기업인 Arm(www.arm.com)이 보급형 모바일 기기에서도 강력한 시각 경험을 제공하는 말리 멀티미디어 제품군(Mali Multimedia Suite)을 발표했다. 이를 통해, 더 많은 모바일 사용자들이 머신러닝(Machine learning, ML)과 HDR, 그리고 복잡한 UI를 지원하는 고급 기능을 즐길 수 있게 됐다.

Arm, 강력한 시각 경험 보편화를 위한 말리 멀티미디어 IP 제품군 발표영국 반도체 설계자산(IP) 기업인 Arm(www.arm.com)이 보급형 모바일 기기에서도 강력한 시각 경험을 제공하는 말리 멀티미디어 제품군(Mali Multimedia Suite)을 발표했다. 이를 통해, 더 많은 모바일 사용자들이 머신러닝(Machine learning, ML)과 HDR, 그리고 복잡한 UI를 지원하는 고급 기능을 즐길 수 있게 됐다. 마이크로칩, 디자인 간소화 구현을 위한 디지털 제어 및 지능형 아날로그 내장 신제품 MCU 출시마이크로컨트롤러, 혼합 신호, 아날로그 반도체 및 플래시-IP 솔루션 분야의 세계적인 리더인 마이크로칩테크놀로지(북아시아 총괄 및 한국 대표: 한병돈)는 고객 혁신에 중점을 두고 설계한 마이크로컨트롤러 제품군 2종을 새롭게 출시했다고 밝혔다.

마이크로칩, 디자인 간소화 구현을 위한 디지털 제어 및 지능형 아날로그 내장 신제품 MCU 출시마이크로컨트롤러, 혼합 신호, 아날로그 반도체 및 플래시-IP 솔루션 분야의 세계적인 리더인 마이크로칩테크놀로지(북아시아 총괄 및 한국 대표: 한병돈)는 고객 혁신에 중점을 두고 설계한 마이크로컨트롤러 제품군 2종을 새롭게 출시했다고 밝혔다.

마이크로칩, 항공우주 및 방위산업 위해 내방사선 MCU 포트폴리오 확장, 32비트 SAMD21RT 출시

마이크로칩, 항공우주 및 방위산업 위해 내방사선 MCU 포트폴리오 확장, 32비트 SAMD21RT 출시 슈퍼마이크로, ISC 2024에서 HPC와 AI 환경에 최적화된 솔루션 선보여…

슈퍼마이크로, ISC 2024에서 HPC와 AI 환경에 최적화된 솔루션 선보여… 마우저, 산업 및 의료, 로봇 애플리케이션을 위한 AMD/자일링스의 크리아(Kria) K24 SOM 공급

마우저, 산업 및 의료, 로봇 애플리케이션을 위한 AMD/자일링스의 크리아(Kria) K24 SOM 공급 인텔, PC간 초고속 전송 가능하게 하는 썬더볼트 쉐어 발표

인텔, PC간 초고속 전송 가능하게 하는 썬더볼트 쉐어 발표 싸이타임, AI 데이터센터를 위한 통합 클럭 칩으로 정밀 타이밍 기술 발전

싸이타임, AI 데이터센터를 위한 통합 클럭 칩으로 정밀 타이밍 기술 발전

- 어플라이드 머티어리얼즈, 회계연도 2024년 2분기 실적 발표

- 엔비디아, 생성형 AI 통해 HPC 연구 가속화

- 자이스, ‘당신에겐 더 선명하게 보입니다’ 신규 캠페인 론칭

- 피커링 인터페이스의 새로운 마이크로웨이브 멀티플렉서 스위치, 최대 40GHz의 대역폭 제공

- 노르딕 세미컨덕터, nRF 클라우드 디바이스 관리 서비스 공식 출시

- AI가 여는 미래 일자리의 변화와 혁신, 마이크로소프트와 링크드인의 2024 업무동향지표

그래픽 / 영상

많이 본 뉴스

한국레노버, AMD 라이젠 스레드리퍼 프로 7000 WX 탑재 ‘씽크스테이션 P8’ 출시

한국레노버, AMD 라이젠 스레드리퍼 프로 7000 WX 탑재 ‘씽크스테이션 P8’ 출시 엔비디아 옴니버스, 차세대 데이터센터 구축 위한 디지털 청사진 공개

엔비디아 옴니버스, 차세대 데이터센터 구축 위한 디지털 청사진 공개 KT, '커스터마이징EZ’로 중소기업 디지털 전환 촉진

KT, '커스터마이징EZ’로 중소기업 디지털 전환 촉진 마이크로칩, 항공기 전기화 전화를 간소화하는 통합 구동 파워 솔루션 출시

마이크로칩, 항공기 전기화 전화를 간소화하는 통합 구동 파워 솔루션 출시 로옴, VCSEL과 LED의 특징을 융합한 적외선 광원 VCSELED 개발

로옴, VCSEL과 LED의 특징을 융합한 적외선 광원 VCSELED 개발 델 테크놀로지스, 파워스케일 스토리지로 AI 데이터 플랫폼 시장 공략

델 테크놀로지스, 파워스케일 스토리지로 AI 데이터 플랫폼 시장 공략 블루투스 지원 기기 출하량, 향후 5년 동안 연평균 8% 성장 전망

블루투스 지원 기기 출하량, 향후 5년 동안 연평균 8% 성장 전망 조시큐리티, 악성코드 정밀 분석 솔루션 조샌드박스 V40 ‘토르말린’ 출시

조시큐리티, 악성코드 정밀 분석 솔루션 조샌드박스 V40 ‘토르말린’ 출시 지멘스-엔비디아, 실시간 몰입형 시각화 위한 생성형 AI 분야 협력 확대

지멘스-엔비디아, 실시간 몰입형 시각화 위한 생성형 AI 분야 협력 확대 오나인솔루션즈, 생성형 AI 기술 적용해 ‘o9 Digital Brain’ 플랫폼 강화

오나인솔루션즈, 생성형 AI 기술 적용해 ‘o9 Digital Brain’ 플랫폼 강화

전 세계 반도체 재료 시장, 2023년 전년 대비 8.2% 하락

전 세계 반도체 재료 시장, 2023년 전년 대비 8.2% 하락 게임 스트리머와 콘텐츠 크리에이터를 위한 추천 아이템 3

게임 스트리머와 콘텐츠 크리에이터를 위한 추천 아이템 3 2024년 1분기 전세계 실리콘 웨이퍼 출하량 5% 감소

2024년 1분기 전세계 실리콘 웨이퍼 출하량 5% 감소