글 / 수르야시 라이(Suryash Rai) 애플리케이션 엔지니어, 아나로그디바이스(Analog Devices)

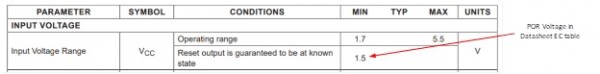

안정적인 수퍼바이저 IC를 사용하면 시스템 안정성을 높이고 전압 트랜션트와 전원 결함에 대한 시스템 신뢰성을 높일 수 있기 때문에 산업계에서는 늘 이에 대한 수요가 있다. 반도체 회사들은 전압 수퍼바이저 IC의 성능을 향상시키기 위해 끊임없이 노력해 왔다. 모든 수퍼바이저 IC는 깨끗하거나 안정적인 리셋(reset) 신호를 발생하기 위해서 파워-온-리셋 전압(VPOR)이라고 하는 최소한의 전압을 필요로 한다. 이 최소 전원 전압에 도달하기 전에 리셋 신호 상태가 불안정할 수 있는데, 이것을 리셋 글리치(glitch on reset)라고 한다.

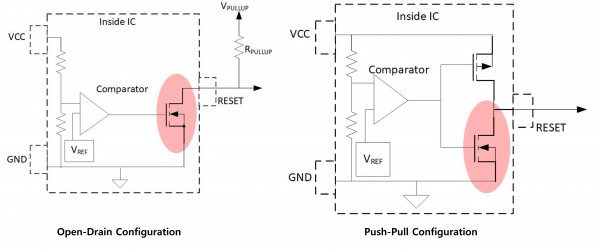

RESET 핀에는오픈 드레인(open-drain)과 푸시-풀(push-pull)이라고 하는 두 가지 토폴로지가 주로 사용된다(그림 1). 두 토폴로지 모두 NMOS를 풀다운 MOSFET으로 사용한다.

그림 1: 리셋 토폴로지로는 오픈 드레인 구성과 푸시-풀 구성이 주로 사용된다.

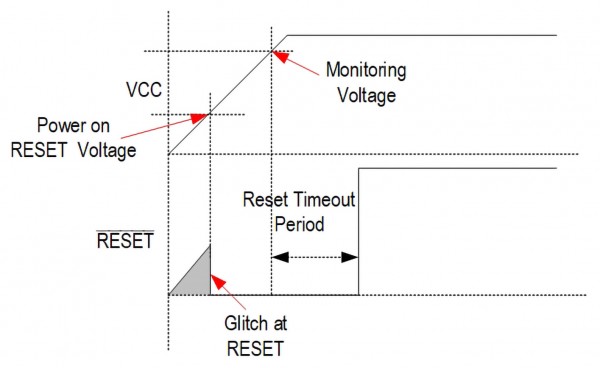

전원이 인가되는 동안, 전원 전압이 VPOR보다 낮으면 내부 회로가 출력 MOSFET을 구동하기에 전압이 충분하지 않으므로 출력 MOSFET이 오프(off)이다. 이 상태에서는 수퍼바이저가 출력 리셋 전압을 제어할 방법이 없다. 리셋은 풀업 전압(VPULLUP)에 비례해서 상승할 것이며, 전원 전압이 VPOR 전압보다 높아지면 내부 MOSFET이 RESET 핀을 유효한 상태로 구동할 것이다.

그림 2: 리셋 신호가 어떻게 풀업 전압(VPULLUP)에 비례하게 상승해서 리셋 글리치를 발생시키는지 알 수 있다.

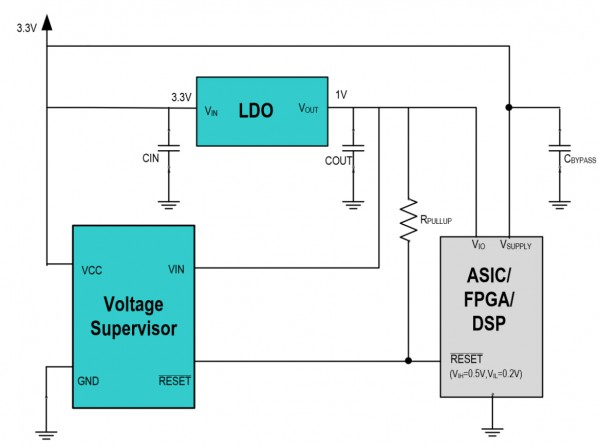

전압 수퍼바이저는 FPGA, ASIC, DSP 등 전압 레일이 1V 정도로 낮은 저전압 레일들을 모니터링하는 용도에 사용될 수 있다. 저전압 프로세서에서는 I/O 로직 레벨이 매우 민감하며, 그림 3에서 보듯이 VIH가 낮게는 0.5V까지 이를 수 있다.

전원 인가 시, 모든 전원 레일이 안정적이 될 때까지 FPGA, ASIC, DSP는 RESET 상태로 있어야 한다. VDD가 VPOR보다 낮으면 RESET에 글리치가 발생하고, 이 글리치가 FPGA에 알 수 없는 동작을 야기할 수 있다. VDD가 VPOR 전압보다 높아지면 내부 MOSFET이 켜지고, RESET을 GND로 연결하고, RESET이 정확한 로직 레벨을 출력하도록 한다.

그림 3: 수퍼바이저가 저전압 ASIC, FPGA, DSP와 어떻게 인터페이싱하는지 보여준다.

그림 4: 리셋 글리치가 발생하는 전원 인가 시퀀스

전자 업계가 저전압 반도체로 옮겨감에 따라서 아날로그 칩 제조사들 역시 기존 수퍼바이저를 가지고 글리치 프리 수퍼바이저를 제공하기 위해서 애쓰고 있다. 하지만 기존의 수퍼바이저로는 프로세스를 개선해서 VPOR 전압을 낮출 수 있을 뿐이어서, 진정한 글리치 프리 수퍼바이저를 제공하기 위해서는 새로운 아키텍처가 필요하다.

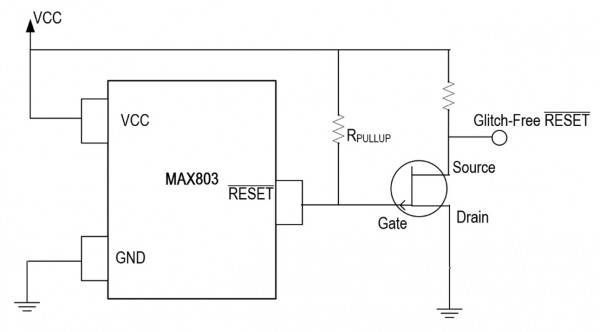

현재로서는 시스템 엔지니어들이 기존의 수퍼바이저에다 외부 회로를 사용해서 글리치 프리 기능을 흉내내는 수준이다(그림 5). 소스-팔로어 구성으로 구성된 표준 JFET을 추가함으로써, 소스의 전압은 ‘VG 전압에서 JFET 임계 전압을 뺀 값’을 따르게 된다. JFET 임계 전압은 VG와 VOUT 사이에서 약 1V 강하를 일으키고, 내부 회로가 작동할 때까지 출력에서 전압 전위 상승을 제거한다.

그림 5: 현행 방식은 기존의 수퍼바이저에다 외부 P-JFET을 추가해서 글리치 프리 기능을 제공하고자 한다.

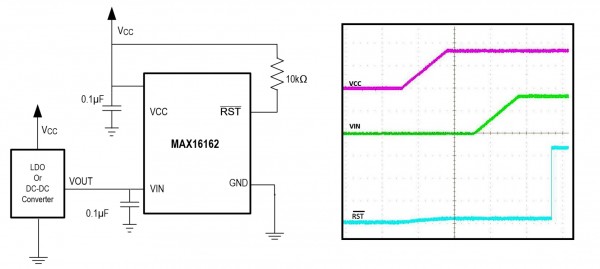

진정한 글리치 프리 수퍼바이저는 리셋을 통해 전류를 싱크해서 제로 VCC에서라도 리셋이 접지 전위가 되도록 한다. 그림 6은 진정한 글리치 프리 수퍼바이저를 사용한 회로를 보여준다. 아나로그디바이스의 MAX16161/MAX16162는 글리치 프리 동작을 위한 외부 부품이 필요 없어 시스템 설계의 크기를 줄이고 비용을 줄일 수 있게 해준다.

그림 6: MAX16162를 사용한 애플리케이션 회로와 해당 타이밍 다이어그램

진정한 글리치 프리 수퍼바이저 IC가 더 이상 컨셉트가 아니라 현실이 되었다. 이제 설계 엔지니어들은 제로 전원 전압에서 안정적인 리셋 신호를 발생하는 수퍼바이저 IC를 활용할 수 있게 되었고, 이 IC로 저전압(1V 이하) 기기들을 모니터링할 수 있게 되었다. MAX16161/MAX16162는 극히 소형화된 nanoPower IC로서, 대기 전류가 825nA에 불과하므로 시스템 배터리 시간을 늘리는 데 도움이 된다.

저자 소개

수르야시 라이(Suryash Rai)는 아나로그디바이스(Analog Devices)에서 2016년부터 애플리케이션 엔지니어로 재직 중이며, 수퍼바이저 및 보호 IC 포트폴리오를 담당하고 있다. 인도 국립 공과대학 카르나타카 캠퍼스에서 통신공학 석사학위를 취득했다. 현재 벵갈로르에 거주하고 있으며, 요리와 여행, 새로운 친구를 사귀는 것을 좋아한다.

저작권©올포칩 미디어. 무단전재 및 재배포를 금지합니다.

스위칭 레귤레이터에서 전류 모드 제어가 중요한 이유스위칭 레귤레이터는 수천 가지 종류의 제품들이 시중에 나와 있으므로 사용자는 입력 전압 범위, 가능한 출력 전압, 최대 출력 전류 같은 사양들을 고려해서 적합한 제품을 선택할 수 있다. 이 글에서는 데이터 시트에서 흔히 거론하는 차별화 기능으로서 전류 모드(current mode) 제어에 대해 설명한다.

스위칭 레귤레이터에서 전류 모드 제어가 중요한 이유스위칭 레귤레이터는 수천 가지 종류의 제품들이 시중에 나와 있으므로 사용자는 입력 전압 범위, 가능한 출력 전압, 최대 출력 전류 같은 사양들을 고려해서 적합한 제품을 선택할 수 있다. 이 글에서는 데이터 시트에서 흔히 거론하는 차별화 기능으로서 전류 모드(current mode) 제어에 대해 설명한다. 자율주행을 위한 자동차 이미징 기술의 발전차량이 초기 ADAS 지원과 운전자 제어 방식에서 완전한 자율주행으로 전환됨에 따라, 이미지 센서의 성능은 점점 더 중요해지고 있다. 특히 모든 도로 이용자들을 안전하게 보호하기 위해 주변 환경을 감지하는 이미저(imager)에서는 이미지 센서가 더욱 중요하다.

자율주행을 위한 자동차 이미징 기술의 발전차량이 초기 ADAS 지원과 운전자 제어 방식에서 완전한 자율주행으로 전환됨에 따라, 이미지 센서의 성능은 점점 더 중요해지고 있다. 특히 모든 도로 이용자들을 안전하게 보호하기 위해 주변 환경을 감지하는 이미저(imager)에서는 이미지 센서가 더욱 중요하다. 스위치 모드 전원장치 보드 레이아웃의 기본 원칙이 글에서는 스위치 모드 전원공급장치(SMPS)를 설계할 때 최적화된 보드 레이아웃을 달성하기 위한 기본적인 원칙들을 설명한다. 잘 설계된 레이아웃은 스위칭 레귤레이터가 안정적으로 작동하도록 할 뿐만 아니라 복사 간섭과 전도 간섭(EMI)을 최소화한다. 스위치 모드 전원장치 설계에서 최적화된 보드 레이아웃을 달성하려면 어떻게 해야 할지 알아본다.

스위치 모드 전원장치 보드 레이아웃의 기본 원칙이 글에서는 스위치 모드 전원공급장치(SMPS)를 설계할 때 최적화된 보드 레이아웃을 달성하기 위한 기본적인 원칙들을 설명한다. 잘 설계된 레이아웃은 스위칭 레귤레이터가 안정적으로 작동하도록 할 뿐만 아니라 복사 간섭과 전도 간섭(EMI)을 최소화한다. 스위치 모드 전원장치 설계에서 최적화된 보드 레이아웃을 달성하려면 어떻게 해야 할지 알아본다. AI 설계의 윤리성, 책임있는 대응 필요인공지능(AI)은 우리의 삶과 일, 그리고 복잡한 문제를 해결하는 방법을 변화시키는 등 인간의 일상 생활에 있어 중요한 부분으로 거듭났다. 신경 질환을 앓고 있는 사람들을 위한 음성 뱅킹 시스템부터 자율주행 차량이 더욱 안전한 주행을 할 수 있도록 지원하고 강수량 패턴과 인구 추세를 더욱 잘 이해하도록 돕는 연구까지, AI는 인간이 마주한 장애물을 극복하고, 더욱 안전한 사회를 만들며, 더 나은 미래를 건설하기 위한 해결책을 개발할 수 있도록 지원한다.

AI 설계의 윤리성, 책임있는 대응 필요인공지능(AI)은 우리의 삶과 일, 그리고 복잡한 문제를 해결하는 방법을 변화시키는 등 인간의 일상 생활에 있어 중요한 부분으로 거듭났다. 신경 질환을 앓고 있는 사람들을 위한 음성 뱅킹 시스템부터 자율주행 차량이 더욱 안전한 주행을 할 수 있도록 지원하고 강수량 패턴과 인구 추세를 더욱 잘 이해하도록 돕는 연구까지, AI는 인간이 마주한 장애물을 극복하고, 더욱 안전한 사회를 만들며, 더 나은 미래를 건설하기 위한 해결책을 개발할 수 있도록 지원한다. PoE 기반 스마트 커넥티드 조명의 혁신PoE 기반 커넥티드 조명은 데이터 네트워크로 제어되고 데이터 케이블을 통해 전원이 공급되는 LED 조명기기를 사용하여 모든 유형의 미래 스마트 빌딩에 가장 유연하고 효율적인 조명 솔루션을 제공한다. 센서, 지능형 조명기기 및 지능형 제어 시스템의 조합을 사용하여 스마트 빌딩은 기존 조명 솔루션으로는 달성할 수 없는 수준의 편안함과 효율성을 제공한다.

PoE 기반 스마트 커넥티드 조명의 혁신PoE 기반 커넥티드 조명은 데이터 네트워크로 제어되고 데이터 케이블을 통해 전원이 공급되는 LED 조명기기를 사용하여 모든 유형의 미래 스마트 빌딩에 가장 유연하고 효율적인 조명 솔루션을 제공한다. 센서, 지능형 조명기기 및 지능형 제어 시스템의 조합을 사용하여 스마트 빌딩은 기존 조명 솔루션으로는 달성할 수 없는 수준의 편안함과 효율성을 제공한다. 미래의 커넥티비티를 혁신하는 와이파이 7와이파이 6E에 이어 IEEE 802.11be 또는 와이파이 7(Wi-Fi 7)이라고 불리는 7세대 와이파이가 곧 발표될 예정이다. 이는 사상 가장 빠른 와이파이 기술로서, 일상에서의 네트워킹과 온라인 활동에 훨씬 더 나은 사용자 경험을 제공하는 게임 체인저가 될 것으로 기대된다. 또한 8K 비디오 스트리밍, 완전 몰입형 AR/VR, 게임, 클라우드 컴퓨팅과 같이 많은 전송 속도를 필요로 하는 애플리케이션들을 가능하게 하고 가속화시킬 것이다.

미래의 커넥티비티를 혁신하는 와이파이 7와이파이 6E에 이어 IEEE 802.11be 또는 와이파이 7(Wi-Fi 7)이라고 불리는 7세대 와이파이가 곧 발표될 예정이다. 이는 사상 가장 빠른 와이파이 기술로서, 일상에서의 네트워킹과 온라인 활동에 훨씬 더 나은 사용자 경험을 제공하는 게임 체인저가 될 것으로 기대된다. 또한 8K 비디오 스트리밍, 완전 몰입형 AR/VR, 게임, 클라우드 컴퓨팅과 같이 많은 전송 속도를 필요로 하는 애플리케이션들을 가능하게 하고 가속화시킬 것이다. 5G 확장을 가속화하는 커넥티드 카레벨 5 완전 자율 자동차가 본격적으로 상용화되기까지는 아직 몇 년이 더 걸릴 것이지만, 앞으로 대부분의 신차는 인터넷 지원이 가능하게 될 것이다. 시장 조사 및 컨설팅 서비스 회사인 P&S 인텔리전스(P&S Intelligence)에 따르면, 전세계 커넥티드 카(Connected Car) 시장이 2019년에 724억 9,920만 달러에서 2025년에 1,984억 5,970만 달러로 24.1%의 CAGR로 성장할 것으로 전망된다. 이러한 성장은 향상된 운전 경험에 대한 소비자들의 요구가 갈수록 높아지면서 계속해서 크기가 축소되고, 가격대가 낮아지는 전자 장치의 발전 덕분에 가속화되고 있다.

5G 확장을 가속화하는 커넥티드 카레벨 5 완전 자율 자동차가 본격적으로 상용화되기까지는 아직 몇 년이 더 걸릴 것이지만, 앞으로 대부분의 신차는 인터넷 지원이 가능하게 될 것이다. 시장 조사 및 컨설팅 서비스 회사인 P&S 인텔리전스(P&S Intelligence)에 따르면, 전세계 커넥티드 카(Connected Car) 시장이 2019년에 724억 9,920만 달러에서 2025년에 1,984억 5,970만 달러로 24.1%의 CAGR로 성장할 것으로 전망된다. 이러한 성장은 향상된 운전 경험에 대한 소비자들의 요구가 갈수록 높아지면서 계속해서 크기가 축소되고, 가격대가 낮아지는 전자 장치의 발전 덕분에 가속화되고 있다. 가정용 의료기기 전원 공급장치에 혁신을 일으키는 질화갈륨 기술병원, 클리닉, 또는 의사 사무실과 같은 전통적인 장소 외에도 점점 더 많은 의료 서비스와 모니터링이 이뤄지고 있다. 이는 이용 가능한 의료 절차의 증가와 의료 서비스를 필요로 하는 노년층의 증가로 이어진 전 세계 인구의 고령화로 인해 임상 공간에 대한 제한이 완화되고 있다.

가정용 의료기기 전원 공급장치에 혁신을 일으키는 질화갈륨 기술병원, 클리닉, 또는 의사 사무실과 같은 전통적인 장소 외에도 점점 더 많은 의료 서비스와 모니터링이 이뤄지고 있다. 이는 이용 가능한 의료 절차의 증가와 의료 서비스를 필요로 하는 노년층의 증가로 이어진 전 세계 인구의 고령화로 인해 임상 공간에 대한 제한이 완화되고 있다. 부스트 컨버터의 근본적 한계 극복 방안이 글에서는 부스트 토폴로지의 근본적인 한계점을 극복하는 방법에 대해 알아본다. 부스트 컨버터를 설계하고 테스트를 해보면 가끔씩 출력 전압이 의도한 것보다 낮게 나타날 수 있다. 부스트 컨버터는 낮은 입력 전압으로부터 높은 출력 전압을 발생하고자 할 때 사용한다. 부스트 토폴로지를 적용한 스위칭 레귤레이터로 이 같은 전압 변환을 손쉽게 달성할 수 있다.

부스트 컨버터의 근본적 한계 극복 방안이 글에서는 부스트 토폴로지의 근본적인 한계점을 극복하는 방법에 대해 알아본다. 부스트 컨버터를 설계하고 테스트를 해보면 가끔씩 출력 전압이 의도한 것보다 낮게 나타날 수 있다. 부스트 컨버터는 낮은 입력 전압으로부터 높은 출력 전압을 발생하고자 할 때 사용한다. 부스트 토폴로지를 적용한 스위칭 레귤레이터로 이 같은 전압 변환을 손쉽게 달성할 수 있다. 손쉬운 갈바닉 절연 구현 방법많은 전자 회로들이 갈바닉 절연을 필요로 한다. 이 전기적 절연을 달성하기 위해서 흔히 트랜스포머를 사용한다. 트랜스포머를 통해 전기 에너지를 전달하는 데에는 다양한 토폴로지를 사용할 수 있다. 주로 50W 미만의 저전력에 널리 사용되는 회로 유형이 ‘플라이백 컨버터(flyback converter)’라고 하는 것이다.

손쉬운 갈바닉 절연 구현 방법많은 전자 회로들이 갈바닉 절연을 필요로 한다. 이 전기적 절연을 달성하기 위해서 흔히 트랜스포머를 사용한다. 트랜스포머를 통해 전기 에너지를 전달하는 데에는 다양한 토폴로지를 사용할 수 있다. 주로 50W 미만의 저전력에 널리 사용되는 회로 유형이 ‘플라이백 컨버터(flyback converter)’라고 하는 것이다. 첨단 운전자 지원 시스템의 역사: 기계 시스템부터 소프트웨어로 운영되는 차량에 이르기까지 (2부)지난 100년 동안 운전자 지원 시스템은 단순한 기계적 크루즈 컨트롤을 시작으로, 소프트웨어 및 메타버스로 알려진 증강/가상 현실에 의해 강화되면서 완전 자율주행 수준의 비전 기술까지 극적으로 발전했다. 2부는 충돌 방지 시스템, 자동 긴급 제동장치(Automatic Emergency Braking, AEB), 백업 카메라, 사각지대 경고, 첨단 전방 조명 및 타이어 공기압 모니터링에 대해 설명한다.

첨단 운전자 지원 시스템의 역사: 기계 시스템부터 소프트웨어로 운영되는 차량에 이르기까지 (2부)지난 100년 동안 운전자 지원 시스템은 단순한 기계적 크루즈 컨트롤을 시작으로, 소프트웨어 및 메타버스로 알려진 증강/가상 현실에 의해 강화되면서 완전 자율주행 수준의 비전 기술까지 극적으로 발전했다. 2부는 충돌 방지 시스템, 자동 긴급 제동장치(Automatic Emergency Braking, AEB), 백업 카메라, 사각지대 경고, 첨단 전방 조명 및 타이어 공기압 모니터링에 대해 설명한다. 첨단 운전자 지원 시스템의 역사: 기계 시스템부터 소프트웨어로 운영되는 차량에 이르기까지 (1부)지난 100년 동안 운전자 지원 시스템은 단순한 기계적 크루즈 컨트롤을 시작으로, 소프트웨어 및 메타버스로 알려진 증강/가상 현실에 의해 강화되면서 완전 자율주행 수준의 비전 기술까지 극적으로 발전했다. 이 글은 ADAS의 역사에 대한 기고문 시리즈의 1부이며, 다양한 시스템에 대해 설명하고 있다. 마지막 시리즈에서는 앞으로의 ADAS 시스템과 더불어 자동차가 어떻게 하나의 기계에서 완전한 디지털 체험기기로 변화될 것인지 설명하려 한다.

첨단 운전자 지원 시스템의 역사: 기계 시스템부터 소프트웨어로 운영되는 차량에 이르기까지 (1부)지난 100년 동안 운전자 지원 시스템은 단순한 기계적 크루즈 컨트롤을 시작으로, 소프트웨어 및 메타버스로 알려진 증강/가상 현실에 의해 강화되면서 완전 자율주행 수준의 비전 기술까지 극적으로 발전했다. 이 글은 ADAS의 역사에 대한 기고문 시리즈의 1부이며, 다양한 시스템에 대해 설명하고 있다. 마지막 시리즈에서는 앞으로의 ADAS 시스템과 더불어 자동차가 어떻게 하나의 기계에서 완전한 디지털 체험기기로 변화될 것인지 설명하려 한다. 필요에 따라 전원라인을 연결 또는 차단하기 위한 단계적 방법과 솔루션어떤 전자 시스템에서는 전원 라인을 차단해야 할 수 있다. 배터리 전하를 낭비하지 않기 위해 배터리 전압을 차단하는 것일 수도 있고, 부하를 전원 라인으로부터 차단하는 것일 수도 있다. 이를 위해서는 기계적 스위치를 사용하는 것이 이상적일 것이다. 하지만 전자 신호에서 스위칭이 일어난다면 전자식 스위치가 좀더 적합할 수 있다. 스위칭 소자로 MOSFET을 사용해서 이러한 전자 스위치를 구현할 수 있다.

필요에 따라 전원라인을 연결 또는 차단하기 위한 단계적 방법과 솔루션어떤 전자 시스템에서는 전원 라인을 차단해야 할 수 있다. 배터리 전하를 낭비하지 않기 위해 배터리 전압을 차단하는 것일 수도 있고, 부하를 전원 라인으로부터 차단하는 것일 수도 있다. 이를 위해서는 기계적 스위치를 사용하는 것이 이상적일 것이다. 하지만 전자 신호에서 스위칭이 일어난다면 전자식 스위치가 좀더 적합할 수 있다. 스위칭 소자로 MOSFET을 사용해서 이러한 전자 스위치를 구현할 수 있다. 무선통신, 레이더, 영상처리, 딥러닝을 위한 FPGA 및 SoC 개발매스웍스는 ‘무선통신, 레이더, 영상처리, 딥러닝을 위한 FPGA 및 SoC 개발’ 온라인 세미나를 개최하고, HDL 코더 및 시뮬링크를 통해 FPGA에 매트랩 알고리즘을 구현하는 워크플로우와 FPGA에서 구동되는 영상처리 및 컴퓨터비전 애플리케이션의 개발 워크플로우, 그리고 무선통신 및 레이더를 위한 FPGA/SoC 구현 예제 등을 선보였다.

무선통신, 레이더, 영상처리, 딥러닝을 위한 FPGA 및 SoC 개발매스웍스는 ‘무선통신, 레이더, 영상처리, 딥러닝을 위한 FPGA 및 SoC 개발’ 온라인 세미나를 개최하고, HDL 코더 및 시뮬링크를 통해 FPGA에 매트랩 알고리즘을 구현하는 워크플로우와 FPGA에서 구동되는 영상처리 및 컴퓨터비전 애플리케이션의 개발 워크플로우, 그리고 무선통신 및 레이더를 위한 FPGA/SoC 구현 예제 등을 선보였다.

데이터브릭스, 기업의 AI 수요 급증에 연 100% 이상 비즈니스 성장 달성 쾌거

데이터브릭스, 기업의 AI 수요 급증에 연 100% 이상 비즈니스 성장 달성 쾌거 전 세계 기업의 63%, 제로 트러스트 전략 도입할 방침

전 세계 기업의 63%, 제로 트러스트 전략 도입할 방침 키사이트, 큐비트 설계를 위한 최초의 통합형 EDA 워크플로우를 제공하는 ‘퀀텀프로’ 출시

키사이트, 큐비트 설계를 위한 최초의 통합형 EDA 워크플로우를 제공하는 ‘퀀텀프로’ 출시 로지텍, 첫 60% 배열 게이밍 키보드 ‘PRO X 60 LIGHTSPEED’ 출시

로지텍, 첫 60% 배열 게이밍 키보드 ‘PRO X 60 LIGHTSPEED’ 출시 지멘스 Simcenter 솔루션, 이모터스의 e-드라이브 소음진동 테스트에 채택

지멘스 Simcenter 솔루션, 이모터스의 e-드라이브 소음진동 테스트에 채택

- 두산디지털이노베이션, ‘AI 시대 HR 전략 수립 위한 포럼’ 개최

- 포티넷, ‘2023 지속가능성 보고서’ 발표

- 마이크로소프트, 국내 비즈니스 혁신 주도하는 AI 트랜스포메이션 사례 공개

- 버티브, 인공지능 기능의 차세대 마이크로 모듈형 데이터센터 출시

- 인섹시큐리티, 암호화폐 분석 디지털 포렌식 솔루션 'TRM 인텔리전스' 출시

- 쿤텍, 자율주행차의 새로운 패러다임 SDV를 위한 실시간 하이퍼바이저 공급

그래픽 / 영상

결정론, 새로운 이더넷 애플리케이션을 열다

결정론, 새로운 이더넷 애플리케이션을 열다 AMD, 새로운 2세대 버설 적응형 SoC로 AI 기반 임베디드 시스템의 종단간 가속 지원

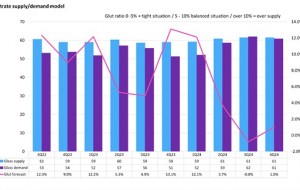

AMD, 새로운 2세대 버설 적응형 SoC로 AI 기반 임베디드 시스템의 종단간 가속 지원 2024년, 디스플레이 글래스 산업 공급부족 우려

2024년, 디스플레이 글래스 산업 공급부족 우려

많이 본 뉴스

AMD, MWC 2024에서 5G 어드밴스드 및 6G AI, vRAN, 오픈RAN 데모 공개

AMD, MWC 2024에서 5G 어드밴스드 및 6G AI, vRAN, 오픈RAN 데모 공개 지멘스-엔비디아, 실시간 몰입형 시각화 위한 생성형 AI 분야 협력 확대

지멘스-엔비디아, 실시간 몰입형 시각화 위한 생성형 AI 분야 협력 확대 마우저, ‘2024 미래를 여는 설계 콘테스트’ 후원

마우저, ‘2024 미래를 여는 설계 콘테스트’ 후원 로지텍, 일렉트로마트 스타필드수원점에 신규 브랜드존 오픈

로지텍, 일렉트로마트 스타필드수원점에 신규 브랜드존 오픈 AMD, 새로운 기업용 AI PC 모바일 및 데스크톱 프로세서 공개

AMD, 새로운 기업용 AI PC 모바일 및 데스크톱 프로세서 공개 취리히 인스트루먼트, 고성능 큐비트 제어를 위한 SHF+ 제품 라인 출시

취리히 인스트루먼트, 고성능 큐비트 제어를 위한 SHF+ 제품 라인 출시 IAR, 르네사스 최초의 범용 RISC-V MCU에 대한 동급 최고의 지원 발표

IAR, 르네사스 최초의 범용 RISC-V MCU에 대한 동급 최고의 지원 발표 R&S EPL1000 EMI 테스트 수신기, 최신 CISPR 14-1 컴플라이언스 테스트 지원

R&S EPL1000 EMI 테스트 수신기, 최신 CISPR 14-1 컴플라이언스 테스트 지원 힐셔, 두 번째로 독일 혁신 기업 TOP 100에 선정

힐셔, 두 번째로 독일 혁신 기업 TOP 100에 선정 마우저, 업계 선도 제조사들의 산업 자동화 제품 공급 확대

마우저, 업계 선도 제조사들의 산업 자동화 제품 공급 확대