전통적인 와이어 본딩 애플리케이션에 사용되는 디바이스와 비교할 때, 플립 칩(flip-chip) 인터커넥트를 갖춘 디바이스는 높은 신호 밀도와 뛰어난 전기적 성능이 필요한 곳에서 널리 사용되는 편이다. 유도성 와이어 본딩이 없는 플립 칩이 인터커넥트로는 가장 적합하지만 칩의 I/O 평면 계획이 제대로 고려되지 않았거나 해당 애플리케이션에 최적화되지 않으면 성능 이점은 순식간에 줄어든다.

예를 들어 50Ω 이하의 송신 회선 임피던스가 요구되고 신호간 누화(crosstalk)가 낮아야 하는 애플리케이션은 이러한 신호를 스트립라인 모드로 전달해야 한다. 스트립라인 라우팅은 스트립라인 모드에서 신호가 칩으로부터 최적으로 빠져나갈 수 있도록 칩 상의 범프를 배열해야 한다. 따라서 칩 상의 I/O 범프를 배열하려면 성능 요구사항을 기반으로 우선 순위를 정할 필요가 있다. 즉, 중요한 신호는 스트립라인으로, 덜 중요한 신호는 마이크로스트립으로 빠져나가도록 해야 한다.

평면 계획을 제대로 세우지 않으면 중요한 신호가 바람직하지 못한 모드로 빠져나가게 되어 결국 신호 성능에 영향을 미친다. 또한 패키지 차원에서도 필요한 것보다 많은 수의 레이어를 기판에 사용하게 되어 제조 원가를 증가시킨다. 이 글에서는 차선의 칩 평면 계획과 관련한 특정 문제점을 중요하게 살펴보고, 성능 문제를 줄이면서 필요한 기판의 레이어 수를 제한하는 기법을 개략적으로 살펴볼 것이다.

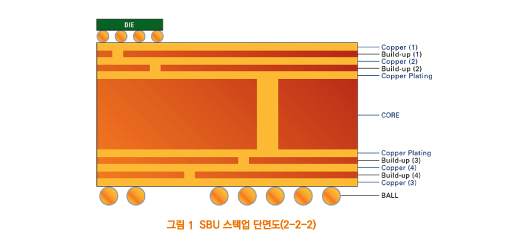

순차 빌드업(SBU) 기판 기술

플립 칩 인터커넥터를 갖는 대부분의 디바이스는 SBU(Sequential Build-Up) 기법을 사용해 제작되는 패키지 기판과 짝을 이룬다. 패키지 기판에는 기존의 기판 제조 과정을 사용해 단일 코어를 회로화한 뒤 더 조밀한 회로층의 빌드업을 위한 바탕으로 사용한다. 유전체(dielectric)층은 코어의 상단과 하단에 대칭으로 놓아 액막(liquid film) 또는 건막(dry film)에 경화의 형태로 응력의 균형을 통해 기계적인 평평함을 유지한다. 그 후 제 위치에 둔 유전체층에 레이저 드릴링을 사용해 비아를 뚫어 층간 회로를 연결한다. 회로는 SAP(semi-additive process) 공법을 사용해 각각의 층 위에 적층한다. 이렇게 순차적으로 유전체와 금속층을 놓는 과정을 통해 기존의 에칭 공정으로는 만들어낼 수 없는 더욱 향상된 지오메트리(최대 12㎛ 트레이스 폭)를 갖춘 금속 트레이스 공정이 가능해진다.

전형적인 SBU 스택업의 단면도는 다음과 같다.

고주파 애플리케이션용 신호 라우팅 최적화

인터커넥트 임피던스를 제어하고 누화를 최소화하는 것은 고주파 애플리케이션의 신호 충실도를 최적화할 때의 주요한 목표다. 시스템이 50Ω 환경에서 작동하도록 설계하면 각각의 송수신기 채널은 그러한 임피던스를 따라야 할 필요가 있다. 그러나 신호 경로를 따라 임피던스에 변화가 발생하면 신호가 지나치게 반사되어 데이터 손상이 발생할 수 있고, 임피던스 변화의 정도에 따라 심할 경우 시스템이 완전히 오류를 일으킬 수도 있다.

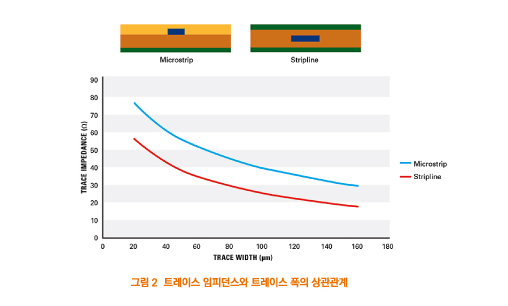

손실이 없는 환경이라고 하면 인터커넥트 임피던스는 전적으로 구조의 인덕턴스와 커패시턴스의 비율을 의미한다. 인덕턴스는 신호 경로 및 리턴 경로가 형성하는 루프 영역이 제어한다. 커패시던트는 보통 트레이스 폭, 리턴 경로까지의 거리, 트레이스와 리턴 경로 사이의 틈을 채운 물질의 유전율에 따라 결정된다. 트레이스 폭이 넓을수록 커패시턴스는 높아지고 임피던스는 낮아지며 트레이스 폭이 좁아지면 그 반대가 된다.

그러면, 마이크로스트립 모드(최외곽층)에서 라우팅을 할 때 SBU 타입 플립 칩 기판에서 50Ω 트레이스를 얻으려면 어떻게 해야 할까? 답은 트레이스 폭을 60㎛로 맞추는 것이다. 60㎛ 폭의 라우팅 트레이스는 기판의 면적을 증가시켜 신호가 I/O 수가 많은 장치의 핀 사이를 효과적으로 빠져나가도록 할 뿐 아니라 신호 트레이스 사이의 라우팅 근접성(routing proximity)을 증가시켜 누화 잡음을 크게 증가시킨다.

해당 애플리케이션에 30Ω 임피던스가 필요할 경우는 어떨까? 실제 트레이스 폭을 사용해 이 정도로 낮은 임피던스를 라우팅하기는 사실상 불가능하다. 마이크로스트립 환경에서 트레이스 커패시턴스는 트레이스의 한 면 위에만 있고 트레이스의 폭에 전적으로 좌우되기 때문이다.

그러나 기판 내에 트레이스를 내장해 스트립라인 모드에서 라우팅을 하면 이 문제를 해결할 수 있다. 스트립라인 환경은 트레이스 양면의 리턴 경로면이 존재해 이를 사용할 수 있기 때문에 동일한 트레이스 폭으로도 효과적으로 용량성 부하를 두 배로 늘리고 훨씬 낮은 임피던스를 달성할 수 있다.

아래의 그래프는 스트립라인과 마이크로스트립 환경일 때 전형적인 SBU 기판에서 라우팅되는 트레이스의 임피던스와 트레이스 폭의 상관관계를 보여준다. 마이크로스트립 모드에서 50Ω 임피던스를 달성하려면 60㎛의 트레이스 폭이 필요하다. 반면 스트립라인 모드에서는 30㎛ 미만의 폭으로도 동일한 임피던스를 얻을 수 있어 라우팅 밀도를 크게 줄이고 누화 성능을 향상시킬 수 있다.

IC 평면 계획 결정

깔끔한 리턴 경로는 트레이스 임피던스를 제어하고 신호 통합에 관련된 문제를 피하는 데 중요하다. 1-2-1 SBU 기판의 경우, 상단 레이어 다음에 양면 코어, 그 다음에 솔더 볼이 부착되는 최종면이 온다. 코어층은 보통 신호 라우팅에는 사용되지 않고 대부분 디바이스의 전원 및 접지를 위해 남겨놓는다. 따라서, 이론적으로는 첫 번째 마이크로스트립층이 유일한 라우팅층이고 시스템에 30 Ω 채널 임피던스가 필요할 때 이런 종류의 기판에서 이 값을 얻기란 사실상 불가능하다.

그림 1에 소개한 것과 같은 2-2-2 기판에서 보이는 또 다른 빌드업 라우팅 레이어에서, 트레이스는 레이어 2에 스트립라인 모드로 내장할 수 있다. 이렇게 하면 낮은 임피던스 라우팅을 확실히 구현할 수 있다.

패드가 한정된 디바이스에서는 피치(pitch)와 I/O 수가 칩의 크기를 결정한다. 물론 칩의 크기가 커지면 비용도 그에 따라 증가한다. 비용을 최적화하기 위해 I/O 핀은 칩의 크기를 줄임과 동시에 동일한 성능을 구현하도록 동심원의 형태로 배열한다. 특정 패드 피치에서 현재 고전압 제작이 갖는 제약으로 인해 SBU 기판의 단일층 상에서는 최대 두 개의 원을 라우팅 할 수 있다. SBU 기판에서 라우팅층을 2개, 3개로 늘이면 원은 4개, 6개로 늘어난다.

예를 들어 4개의 I/O 동심원이 있는 디바이스라면 최소한 3-2-3 SBU 기판이 필요하다. 바깥의 원 2개는 마이크로스트립 모드에서 기판 스택업의 레이어1에서 빠져나간다. 레이어 1의 라우팅에 깨끗한 레퍼런스를 제공하기 위해서는 보통 레이어2를 리턴 경로로 남겨두어야 한다. 그러면 레이어3은 다시 라우팅 층으로 사용할 수 있고 네 번째 층은 기판의 코어에 속하게 된다. 3-2-3 스택업은 칩 상의 I/O 핀에 대해 효과적으로 2개의 라우팅 층을 제공해 패키지 볼을 빠져나가고 이에 연결될 수 있도록 한다. 낮은 임피던스가 필요한 트레이스가 내부 층의 라우팅에 가장 적합한 것은 틀림 없다. 그러나 관련된 I/O 범프(칩 상의 연결)가 칩의 외부에 있으면 마이크로스트립 모드에서 이들을 라우팅하기는 거의 불가능하며 원하는 만큼의 낮은 임피던스를 구현하는 것 역시 사실상 불가능하다. 그러므로 이들을 스트립라인 모드에서 내장해야 한다.

동일한 I/O 평면 계획을 사용하되 스트립라인 모드에서 I/O의 바깥 줄을 만들고 싶다면 SBU 기판은 4-2-4 스택업이어야 한다. 레이어1 은 리턴 경로용, 레이어2는 낮은 임피던스 트레이스 라우팅용, 레이어3은 또 다른 리턴 경로용, 레이어4는 또 다른 신호 라우팅 및 코어층으로 사용하는 것이다. 그러나 그렇게 하면 동일한 I/O 평면 계획으로 SBU 기판의 층 수가 증가해 패키지 비용이 크게 증가한다.

그러나 칩의 평면 계획을 낮은 임피던스 라우팅이 필요한 I/O를 바깥의 두 동심원 대신 내부의 두 동심원에 두면 기판 라우팅 층을 추가할 필요가 없어져 패키지 비용을 낮추고 원하는 신호 성능을 구현할 수 있다.

결론적으로 이런 단순한 연습을 통해 칩의 평면 계획을 잘 알고 시스템을 구성하는 일이 얼마나 중요한지에 대한 사고 과정을 거치게 되고, 그와 동시에 제품 성능을 최적화하고 비용을 최소화하기 위해서는 IC 설계 및 패키징 팀 간의 상호 설계 과정이 중요하다는 것도 다시 한 번 알게 된다. 각각의 부품을 시스템에 매끄럽게 통합하기 위해서는 패키지-PCB 인터페이스에서 이와 같은 평면 계획 결정의 중요성을 인식하고 설계를 하는 것이 필요하다.

저작권©올포칩 미디어. 무단전재 및 재배포를 금지합니다.

최신 고속 RF 트랜시버 설계를 지원하는 개발 에코시스템컨버터가 RF 프런트엔드에 다가갈수록 부품과 기능, 폭넓은 개발 에코시스템에 대한 엄격한 요건들이 새롭게 생겨난다.

최신 고속 RF 트랜시버 설계를 지원하는 개발 에코시스템컨버터가 RF 프런트엔드에 다가갈수록 부품과 기능, 폭넓은 개발 에코시스템에 대한 엄격한 요건들이 새롭게 생겨난다. 매우 낮은 인덕터 DCR 감지와 빠른 과도 응답, 위상당 30A를 제공하는 고효율 다상 전원LTC3875는 최신 고속, 고용량 데이터 프로세싱 시스템, 텔레콤 시스템, 산업 장비 및 DC 전력 분배 시스템의 전력 밀도 요건을 만족하는 다양한 기능의 듀얼 출력 동기식 벅 컨트롤러이다.

매우 낮은 인덕터 DCR 감지와 빠른 과도 응답, 위상당 30A를 제공하는 고효율 다상 전원LTC3875는 최신 고속, 고용량 데이터 프로세싱 시스템, 텔레콤 시스템, 산업 장비 및 DC 전력 분배 시스템의 전력 밀도 요건을 만족하는 다양한 기능의 듀얼 출력 동기식 벅 컨트롤러이다.  최상의 가치와 최적화를 실현한 자일링스의 올 프로그래머블 로우-엔드 포트폴리오비용에 민감한 애플리케이션을 위해 최신 올 프로그래머블(All Programmable) 디바이스는 새로운 차원의 정교하면서도 다양한 요건을 만족해야 한다. 컨수머 및 자동차, 산업 및 의료, 통신 분야의 저가 시스템들은 와트 당 최고 성능은 물론, 첨단 프로세싱을 위한 프로그래머블 로직 디바이스를 필요로 할 수도 있으며, 혹은 간단하게 기능 브리징 만을 필요로 할 수 있다.

최상의 가치와 최적화를 실현한 자일링스의 올 프로그래머블 로우-엔드 포트폴리오비용에 민감한 애플리케이션을 위해 최신 올 프로그래머블(All Programmable) 디바이스는 새로운 차원의 정교하면서도 다양한 요건을 만족해야 한다. 컨수머 및 자동차, 산업 및 의료, 통신 분야의 저가 시스템들은 와트 당 최고 성능은 물론, 첨단 프로세싱을 위한 프로그래머블 로직 디바이스를 필요로 할 수도 있으며, 혹은 간단하게 기능 브리징 만을 필요로 할 수 있다.  NFC 기술을 통한 소비자 마케팅의 변화NXP는 향후 몇 년 내에 NFC가 우리 일상 생활에 상당한 변화를 가지고 올 것으로 기대하고 있다. 이는 시장 수치들만 봐도 충분히 짐작할 수 있다. 통신거리 100m 이상의 NFC 기반 단말기 제품들이 2012년에 상용화되었는데, ABI 리서치의 조사에 따르면 2014년경에는 NFC 단말기의 보급률이 5억대를 초과하여 2017년경에는 20억 대에 이를 것으로 전망되고 있다.

NFC 기술을 통한 소비자 마케팅의 변화NXP는 향후 몇 년 내에 NFC가 우리 일상 생활에 상당한 변화를 가지고 올 것으로 기대하고 있다. 이는 시장 수치들만 봐도 충분히 짐작할 수 있다. 통신거리 100m 이상의 NFC 기반 단말기 제품들이 2012년에 상용화되었는데, ABI 리서치의 조사에 따르면 2014년경에는 NFC 단말기의 보급률이 5억대를 초과하여 2017년경에는 20억 대에 이를 것으로 전망되고 있다. 32비트 MCU 플랫폼 간의 마이그레이션지난 수년간, 단일 코어 플랫폼의 표준화를 통해 마이크로컨트롤러(MCU) 공급업체 간 디자인 마이그레이션을 간소화하기 위한 논의가 이루어져 왔다. 흥미로운 사실은 이 모든 논의 가운데 주변장치에 대한 언급이 없다는 것이다. 주변장치는 MCU 공급업체 간 애플리케이션 마이그레이션을 위하여 반드시 필요한 요소이다.

32비트 MCU 플랫폼 간의 마이그레이션지난 수년간, 단일 코어 플랫폼의 표준화를 통해 마이크로컨트롤러(MCU) 공급업체 간 디자인 마이그레이션을 간소화하기 위한 논의가 이루어져 왔다. 흥미로운 사실은 이 모든 논의 가운데 주변장치에 대한 언급이 없다는 것이다. 주변장치는 MCU 공급업체 간 애플리케이션 마이그레이션을 위하여 반드시 필요한 요소이다. 첨단 다상 인터리빙 부스트 컨버터를 위한 빠르고 간단한 솔루션2상 인터리빙 부스트 컨버터가 단상 컨버터에 비해 갖는 장점은 고효율 다상 인터리빙 컨버터에 대한 연구를 가속화시켰다. 2상 인터리빙 부스트 컨버터는 기존의 단일 대형 스테이지에 비해 보다 작은 2개의 스테이지를 병렬로 관리할 수 있다.

첨단 다상 인터리빙 부스트 컨버터를 위한 빠르고 간단한 솔루션2상 인터리빙 부스트 컨버터가 단상 컨버터에 비해 갖는 장점은 고효율 다상 인터리빙 컨버터에 대한 연구를 가속화시켰다. 2상 인터리빙 부스트 컨버터는 기존의 단일 대형 스테이지에 비해 보다 작은 2개의 스테이지를 병렬로 관리할 수 있다.  LED 가로등을 위한 두 개의 스위치를 가지는 플라이백 컨버터LED는 기존 광원들에 비해 효율과 수명이 우수하여 에너지 절약을 위한 차세대 조명으로 각광받고 있다. 고효율과 장수명은 가로등에도 아주 중요한 요소이며 LED의 적용이 기대되는 분야 중 하나이다.

LED 가로등을 위한 두 개의 스위치를 가지는 플라이백 컨버터LED는 기존 광원들에 비해 효율과 수명이 우수하여 에너지 절약을 위한 차세대 조명으로 각광받고 있다. 고효율과 장수명은 가로등에도 아주 중요한 요소이며 LED의 적용이 기대되는 분야 중 하나이다.  SoC FPGA를 이용한 차량용 레이더 디지털 연산 기능 구현 방법최근 레이더가 주차 보조 및 차선 이탈 경고 등을 위해 고가 차량용 플랫폼에 적용되기 시작했다. 이들 애플리케이션은 능동 충돌 방지 및 적응형 크루즈 컨트롤 등을 포함하며 지속적으로 확대될 것이다. 거리, 속도, 방향을 결정하기 위한 레이더 신호의 디지털 신호 처리 기능은 SoC FPGA를 사용하는 것이 이상적이다.

SoC FPGA를 이용한 차량용 레이더 디지털 연산 기능 구현 방법최근 레이더가 주차 보조 및 차선 이탈 경고 등을 위해 고가 차량용 플랫폼에 적용되기 시작했다. 이들 애플리케이션은 능동 충돌 방지 및 적응형 크루즈 컨트롤 등을 포함하며 지속적으로 확대될 것이다. 거리, 속도, 방향을 결정하기 위한 레이더 신호의 디지털 신호 처리 기능은 SoC FPGA를 사용하는 것이 이상적이다. NFC 규격을 준수하는 소자를 구현하기 위한 새롭고 경제적인 방법근거리 무선통신(NFC) 기술을 갖춘 소자들 설치가 기하급수적으로 증가하고 있어 향후 18 개월 내에 많은 시판 스마트폰들의 표준 기능이 될 것으로 보인다. 이제 거의 모든 종류의 다른 전자 기기 제조업체들이 사용자들의 제품을 NFC를 통해 스마트폰에 손쉽게 무선 연결하도록 해줌으로써 사용자 경험을 개선할 기회를 제공하고 있다. 그러나 시스템 설계자들에게 주어진 문제는'그 실제적인 구현 방법은 무엇인가 하는 것이다.

NFC 규격을 준수하는 소자를 구현하기 위한 새롭고 경제적인 방법근거리 무선통신(NFC) 기술을 갖춘 소자들 설치가 기하급수적으로 증가하고 있어 향후 18 개월 내에 많은 시판 스마트폰들의 표준 기능이 될 것으로 보인다. 이제 거의 모든 종류의 다른 전자 기기 제조업체들이 사용자들의 제품을 NFC를 통해 스마트폰에 손쉽게 무선 연결하도록 해줌으로써 사용자 경험을 개선할 기회를 제공하고 있다. 그러나 시스템 설계자들에게 주어진 문제는'그 실제적인 구현 방법은 무엇인가 하는 것이다. 유도 가열 애플리케이션의 IGBT 전력손실 최소화최근 들어 사용되고 있는 전기기구 수가 늘어나면서 서구 국가 대부분 및 개발도상국의 일반 가정 내 총 에너지 소모가 꾸준히 증가하게 되었다. 연료 자원이 더욱 부족해짐에 따라 이러한 에너지 소모와 관련된 비용도 증가했으며, 그 결과 전력 업체들은 요금을 인상하고 있다. 전력망에서 얻는 전력량을 극대화하여 전기요금을 억제하고 탄소 배출도 낮추기 위해서는 보다 에너지 효율적인 기기들을 개발하는 데 더 많은 노력을 기울여야 한다.

유도 가열 애플리케이션의 IGBT 전력손실 최소화최근 들어 사용되고 있는 전기기구 수가 늘어나면서 서구 국가 대부분 및 개발도상국의 일반 가정 내 총 에너지 소모가 꾸준히 증가하게 되었다. 연료 자원이 더욱 부족해짐에 따라 이러한 에너지 소모와 관련된 비용도 증가했으며, 그 결과 전력 업체들은 요금을 인상하고 있다. 전력망에서 얻는 전력량을 극대화하여 전기요금을 억제하고 탄소 배출도 낮추기 위해서는 보다 에너지 효율적인 기기들을 개발하는 데 더 많은 노력을 기울여야 한다. 완벽한 노이즈 킬러, 싸이프레스의 Gen5 트루터치 컨트롤러초박형 0.5mm 커버 렌즈와 최고 22mm의 손가락 크기로 1~500kHz까지 1KHz 단위로 측정된 충전 노이즈 면역성에서 전례없는 40Vpp 내성을 달성한 싸이프레스의 새로운 Gen5 트루터치(TrueTouch) 컨트롤러가 출시됐다. 현재까지 어떠한 컨트롤러도 이러한 조건하에서 15Vpp 이상의 노이즈 내성을 달성하지 못했다.

완벽한 노이즈 킬러, 싸이프레스의 Gen5 트루터치 컨트롤러초박형 0.5mm 커버 렌즈와 최고 22mm의 손가락 크기로 1~500kHz까지 1KHz 단위로 측정된 충전 노이즈 면역성에서 전례없는 40Vpp 내성을 달성한 싸이프레스의 새로운 Gen5 트루터치(TrueTouch) 컨트롤러가 출시됐다. 현재까지 어떠한 컨트롤러도 이러한 조건하에서 15Vpp 이상의 노이즈 내성을 달성하지 못했다.  올프로그래머블 다중-모드 무선: 보다 적은 부품으로 다중 표준, 다중 대역 요구에 대응증가하는 커버리지 및 수용 능력에 대한 요구는 펨토셀 및 피코셀, 마이크로셀, 매크로셀, 액티브 안테나 시스템을 모두 포괄하는 이종 네트워크에서 빠르게 확장되고 있다. 또한 다중 표준 및 주파수, 대역폭 지원은 상업용 무선 분야에서 보다 뛰어난 유연성을 요건을 더욱 강화시키고 있다.

올프로그래머블 다중-모드 무선: 보다 적은 부품으로 다중 표준, 다중 대역 요구에 대응증가하는 커버리지 및 수용 능력에 대한 요구는 펨토셀 및 피코셀, 마이크로셀, 매크로셀, 액티브 안테나 시스템을 모두 포괄하는 이종 네트워크에서 빠르게 확장되고 있다. 또한 다중 표준 및 주파수, 대역폭 지원은 상업용 무선 분야에서 보다 뛰어난 유연성을 요건을 더욱 강화시키고 있다. - 싱글칩 배터리 관리 솔루션 발표자료

- 브로드컴의 3G 폰 온 어 칩 발표자료유무선 통신용 반도체 분야의 글로벌 선도기업인 브로드컴은 기자회견에서 3G 셀룰러와 모바일 관련 핵심 기능을 초 저전력 싱글 65나노미터 CMOS 다이에 통합시킨 ‘3G 폰 온 어 칩’ 솔루션과 고화질•초절전형 모바일 멀티미디어 아키텍처인 ‘브로드컴 비디오코어3(Broadcom® VideoCore® III)’ 와 비디오코어3 기반의 모바일 HD멀티미디어 프로세서 ‘BCM2727’솔루션을 발표했다.

IMDT와 Hailo가 합작하여 최고의 실시간 성능을 위한 엣지 AI 솔루션 출시

IMDT와 Hailo가 합작하여 최고의 실시간 성능을 위한 엣지 AI 솔루션 출시 콩가텍, 인텔 코어 i3 및 인텔 아톰 x7000RE 프로세서 탑재 SMARC 모듈 출시

콩가텍, 인텔 코어 i3 및 인텔 아톰 x7000RE 프로세서 탑재 SMARC 모듈 출시 인텔, 세계 최대규모 뉴로모픽 시스템 공개

인텔, 세계 최대규모 뉴로모픽 시스템 공개 마이크로칩, 항공기 전기화 전화를 간소화하는 통합 구동 파워 솔루션 출시

마이크로칩, 항공기 전기화 전화를 간소화하는 통합 구동 파워 솔루션 출시 텔레다인르크로이, 광범위한 통신 기술 데이터를 원활하게 포착하는 프론트라인 X500e 출시

텔레다인르크로이, 광범위한 통신 기술 데이터를 원활하게 포착하는 프론트라인 X500e 출시

- TTTech Auto, 복잡한 소프트웨어 통합을 혁신할 차세대 스케줄러 ‘MotionWise Schedule’ 출시

- 아이스아이, 글로벌 SAR 리더십 확장을 위한 기업의 성장 펀딩 라운드 초과 달성

- 오나인솔루션즈, 생성형 AI 기술 적용해 ‘o9 Digital Brain’ 플랫폼 강화

- 테스트웍스, 차세대 반도체 개발 지원 시험-검증 통합 관리 솔루션 발표

- NXP, 안전한 SDV 중앙 제어 위한 차량용 S32N55 프로세서 출시

- 팔로알토 네트웍스, AI 시대의 사이버 보안 주제로 ‘이그나이트 2024’ 행사 개최

그래픽 / 영상

결정론, 새로운 이더넷 애플리케이션을 열다

결정론, 새로운 이더넷 애플리케이션을 열다 AMD, 새로운 2세대 버설 적응형 SoC로 AI 기반 임베디드 시스템의 종단간 가속 지원

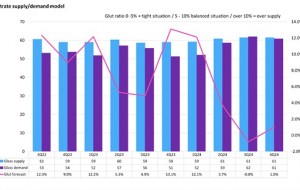

AMD, 새로운 2세대 버설 적응형 SoC로 AI 기반 임베디드 시스템의 종단간 가속 지원 2024년, 디스플레이 글래스 산업 공급부족 우려

2024년, 디스플레이 글래스 산업 공급부족 우려

많이 본 뉴스

자이스 코리아, KOREA LAB 2024에서 현미경 분야 혁신적 자동화 솔루션 선보여

자이스 코리아, KOREA LAB 2024에서 현미경 분야 혁신적 자동화 솔루션 선보여 네패스, 지멘스의 첨단 설계 솔루션으로 3D-IC 시대를 위한 IC 패키징 역량 확장

네패스, 지멘스의 첨단 설계 솔루션으로 3D-IC 시대를 위한 IC 패키징 역량 확장 버티브, 김성엽 신임 한국 사장 선임

버티브, 김성엽 신임 한국 사장 선임 지멘스, ‘아이온 모빌리티’ 개발 지원으로 동남아 전기 바이크 시장 확대

지멘스, ‘아이온 모빌리티’ 개발 지원으로 동남아 전기 바이크 시장 확대 로데슈바르즈, 가장 컴팩트한 상용 3GPP 5G 적합성 테스트 솔루션 공개

로데슈바르즈, 가장 컴팩트한 상용 3GPP 5G 적합성 테스트 솔루션 공개 KT, 노바테크와 손잡고 물류로봇 플랫폼 사업 추진

KT, 노바테크와 손잡고 물류로봇 플랫폼 사업 추진 Qt그룹, 퀄컴과 협력해 산업용 IoT 기기 UI 개발 간소화

Qt그룹, 퀄컴과 협력해 산업용 IoT 기기 UI 개발 간소화 삼텍, DC~67GHz의 좁은 바디 RF 에지 론치 커넥터 출시

삼텍, DC~67GHz의 좁은 바디 RF 에지 론치 커넥터 출시 헥사곤-한서대학교, 차세대 SW융합 인재 양성 위한 MOU 체결

헥사곤-한서대학교, 차세대 SW융합 인재 양성 위한 MOU 체결 로데슈바르즈와 오토톡스, 세계 최초 5G-V2X 칩셋 검증을 위해 협력

로데슈바르즈와 오토톡스, 세계 최초 5G-V2X 칩셋 검증을 위해 협력