래티스 반도체(Lattice Semiconductor)가 자사의 FPGA 설계용 소프트웨어 툴 최신 버전인 Lattice Radiant 2.0을 출시한다고 밝혔다. 새롭게 업데이트된 이 설계 툴은 래티스의 새로운 CrossLink-NX FPGA 제품군 같이 보다 높은 밀도의 디바이스들을 지원할 뿐 아니라, 래티스 FPGA 기반 시스템을 보다 쉽고 빠르게 개발할 수 있게 하는 새로운 특징들을 제공한다.

시스템 개발자가 하드웨어 플랫폼을 평가할 때, 사실 하드웨어는 선택을 위한 여러 가지 기준 중 일부일 뿐이다. 개발자들은 해당 하드웨어를 구성할 때 사용하는 설계 소프트웨어 역시 사용 편의성, 지원 기능 등을 기준으로 평가한다. 이러한 특성들이 전반적인 시스템 개발 시간과 비용에 상당한 영향을 미치기 때문이다.

래티스 반도체의 로저 두(Roger Do) 소프트웨어 담당 선임 제품 라인 매니저는 “래티스 Radiant 2.0 설계 소프트웨어는 개발자들에게 쉽게 따라 할 수 있는 사용자 경험을 제공한다”며, “이 툴은 설계 기획 단계부터 IP 이식, 구현, 비트스트림 생성, FPGA에 비트스트림을 다운로드하기까지의 일련의 설계 흐름에 걸쳐 사용자를 이끌어준다. 심지어 FPGA를 다뤄본 경험이 전혀 없는 개발자라도 래티스 Radiant의 자동화 기능을 쉽게 활용할 수 있다. 숙련된 FPGA 개발자인 경우, 특별한 최적화 작업이 필요하다면 새로운 래티스 Radiant 2.0을 활용해 FPGA 설정을 보다 정교하게 제어할 수 있다”고 말했다.

Radiant 2.0은 사용자가 실시간으로 버그를 수정할 수 있게 해주는 온칩 디버깅 툴이 새롭게 업그레이드 되었다. 새로운 디버깅 기능을 활용하여 개발자는 가상의 스위치나 LED를 자신의 코드에 심어 작업의 성공 여부를 확인할 수 있다. 또한 이 툴을 활용해 사용자는 서로 다른 동작 모드를 시험하기 위해 하드 IP 블록 설정을 변경할 수 있다.

이외에도 향상된 타이밍 분석 기능을 통해 보다 정확한 추적 및 라우팅 플래닝과 클럭 타이밍을 제공하여 설계 혼잡과 열 관련 이슈들을 방지할 수 있도록 해준다. 설계 변경 주문(Engineering Change Order, ECO) 편집기는 개발자가 전체 FPGA 데이터베이스를 재컴파일 할 필요 없이, 최종 설계까지 변경 사항을 누적 적용할 수 있도록 해준다. 또한 동시 스위칭 출력(Simultaneous Switching Output, SSO) 계산기는 개별 핀의 신호 무결성을 분석함으로써 다른 핀과의 근접성이 각 핀의 성능에 부정적인 영향을 미치지 않도록 보장한다.

저작권©올포칩 미디어. 무단전재 및 재배포를 금지합니다.

ST, 스마트 계량기 칩셋에 무선기능 추가해 보다 유연하고 확장 가능한 스마트 인프라 지원스마트 전기 계량기에 이미 널리 사용되고 있는 ST의 ST8500 전력선 통신(PLC: Powerline Communication) 칩셋이 기존의 전력 케이블이나 무선 주파수(RF) 웨이브를 통해 스마트 계량기와 통신이 가능하도록 두 가지 연결 기능을 모두 결합해 성능을 강화했다

ST, 스마트 계량기 칩셋에 무선기능 추가해 보다 유연하고 확장 가능한 스마트 인프라 지원스마트 전기 계량기에 이미 널리 사용되고 있는 ST의 ST8500 전력선 통신(PLC: Powerline Communication) 칩셋이 기존의 전력 케이블이나 무선 주파수(RF) 웨이브를 통해 스마트 계량기와 통신이 가능하도록 두 가지 연결 기능을 모두 결합해 성능을 강화했다 ADI, 쿼드 출력 DC/DC µModule 레귤레이터 출시2.7V ~ 17V의 입력 전압 범위에서 동작하는 LTM4668과 LTM4668A는 0.6V ~ 5.5V의 출력 전압 범위를 제공한다. 새로운 디바이스는 주파수 동기화, 다중 위상(PolyPhase) 동작, 선택가능한 버스트모드(Burst Mode) 동작, 100% 듀티 사이클, 낮은 IQ 동작을 지원한다. 높은 스위칭 주파수와 전류 모드 아키텍처 덕분에, 라인 및 부하 변화가 발생해도 안정성을 유지하면서 매우 신속한 과도 응답 특성을 나타낸다.

ADI, 쿼드 출력 DC/DC µModule 레귤레이터 출시2.7V ~ 17V의 입력 전압 범위에서 동작하는 LTM4668과 LTM4668A는 0.6V ~ 5.5V의 출력 전압 범위를 제공한다. 새로운 디바이스는 주파수 동기화, 다중 위상(PolyPhase) 동작, 선택가능한 버스트모드(Burst Mode) 동작, 100% 듀티 사이클, 낮은 IQ 동작을 지원한다. 높은 스위칭 주파수와 전류 모드 아키텍처 덕분에, 라인 및 부하 변화가 발생해도 안정성을 유지하면서 매우 신속한 과도 응답 특성을 나타낸다. 오토데스크, 엔비디아 RTX 기반의 GPU 탑재한 ‘아놀드 6’ 출시아놀드 GPU를 탑재한 아놀드 6는 룩(look) 개발부터 최종 프레임 렌더링에 이르기까지, 아티스트 및 스튜디오가 콘텐츠를 생성하고 반복하는 작업을 단순화한다. 이를 통해, 빠른 속도로 진행되는 작업환경에 적응할 수 있는 속도와 유연성을 제공할 뿐 아니라, 렌더링 용량을 확장시켜 제작흐름의 변화를 수용할 수 있도록 한다.

오토데스크, 엔비디아 RTX 기반의 GPU 탑재한 ‘아놀드 6’ 출시아놀드 GPU를 탑재한 아놀드 6는 룩(look) 개발부터 최종 프레임 렌더링에 이르기까지, 아티스트 및 스튜디오가 콘텐츠를 생성하고 반복하는 작업을 단순화한다. 이를 통해, 빠른 속도로 진행되는 작업환경에 적응할 수 있는 속도와 유연성을 제공할 뿐 아니라, 렌더링 용량을 확장시켜 제작흐름의 변화를 수용할 수 있도록 한다. 피렐리(Pirelli), 오나인(o9) 솔루션즈의 ‘SCM SaaS 플랫폼’ 도입피렐리(Pirelli)는 차세대 기술로 공급망 성능을 향상시키는 디지털화 전략(Digitalization Strategy) 프로젝트를 추진해왔다. 오나인(o9)은 짧은 가치실현시간(time-to-value)과 장기적인 유연성을 제공하는 통합 엔드-투-엔드 플랫폼을 무기로 진화하는 비즈니스 요구사항에 원활히 대응하는 전략을 추진해왔는데, 이 같은 장점을 높이 평가한 피렐리(Pirelli)는 디지털 전환 여정(digital transformation journey)의 파트너로서 오나인(o9)을 최종 채택했다.

피렐리(Pirelli), 오나인(o9) 솔루션즈의 ‘SCM SaaS 플랫폼’ 도입피렐리(Pirelli)는 차세대 기술로 공급망 성능을 향상시키는 디지털화 전략(Digitalization Strategy) 프로젝트를 추진해왔다. 오나인(o9)은 짧은 가치실현시간(time-to-value)과 장기적인 유연성을 제공하는 통합 엔드-투-엔드 플랫폼을 무기로 진화하는 비즈니스 요구사항에 원활히 대응하는 전략을 추진해왔는데, 이 같은 장점을 높이 평가한 피렐리(Pirelli)는 디지털 전환 여정(digital transformation journey)의 파트너로서 오나인(o9)을 최종 채택했다.- 블랙베리 QNX 하이퍼바이저, 자동차안전무결성등급 최고등급 획QNX Hypervisor for Safety 2.0은 개발자들이 인포테인먼트와 같이 안전이 크게 중요하지 않은 시스템과 차체 도메인 컨트롤러와 같이 안전이 중요한 시스템을 분리하고, 시스템 장애 시 중요 시스템을 격리하여 안전하게 관리할 수 있도록 지원한다.

마이크로칩, PolarFire SoC FPGA 제품군 세부 사항 공개 및 조기 이용 프로그램(EAP) 발표PolarFire SoC는 업계 경쟁 디바이스 대비 최고 50% 낮은 소비전력을 갖는 등 우수한 전력효율을 자랑한다. 이를 통해 팬과 방열판의 필요성을 없애 재료비를 절감하는 등 고객에게 수많은 혜택을 제공한다. 이 제품은 결정적이고 일관성 높은 RISC-V CPU 클러스터와 리눅스 및 실시간 애플리케이션을 지원하는 결정론적 L2 메모리 서브시스템을 갖춘 최초의 SoC FPGA이다.

마이크로칩, PolarFire SoC FPGA 제품군 세부 사항 공개 및 조기 이용 프로그램(EAP) 발표PolarFire SoC는 업계 경쟁 디바이스 대비 최고 50% 낮은 소비전력을 갖는 등 우수한 전력효율을 자랑한다. 이를 통해 팬과 방열판의 필요성을 없애 재료비를 절감하는 등 고객에게 수많은 혜택을 제공한다. 이 제품은 결정적이고 일관성 높은 RISC-V CPU 클러스터와 리눅스 및 실시간 애플리케이션을 지원하는 결정론적 L2 메모리 서브시스템을 갖춘 최초의 SoC FPGA이다. AMD, 라데온 소프트웨어 아드레날린 2020 에디션 공개AMD 라데온 소프트웨어 아드레날린 2020 에디션은 완전히 재설계된 게임 애플리케이션을 특징으로 게이머들에게 강력한 기능을 제공한다. 새로운 라데온 부스트(Radeon Boost) 기능은 빠른 동작의 게임 플레이에 향상된 성능과 부드러운 환경을 제공하고, 새로운 인티저 디스플레이 스케일링(Integer Display Scaling) 기술은 최신 디스플레이에 맞춰 오래된 게임에 활력을 불어넣는다.

AMD, 라데온 소프트웨어 아드레날린 2020 에디션 공개AMD 라데온 소프트웨어 아드레날린 2020 에디션은 완전히 재설계된 게임 애플리케이션을 특징으로 게이머들에게 강력한 기능을 제공한다. 새로운 라데온 부스트(Radeon Boost) 기능은 빠른 동작의 게임 플레이에 향상된 성능과 부드러운 환경을 제공하고, 새로운 인티저 디스플레이 스케일링(Integer Display Scaling) 기술은 최신 디스플레이에 맞춰 오래된 게임에 활력을 불어넣는다. 래티스, 임베디드 비전 및 엣지 AI에 최적화된 CrossLink-NX FPGA 출시5G 커넥티비티, 클라우드 기반 분석, 공장 자동화, 스마트 홈 같은 최신 기술들이 머신러닝을 지원하는 임베디드 비전 솔루션에 대한 수요를 이끌고 있다. 하지만 데이터 지연, 비용, 개인정보 이슈 등 클라우드 기반 머신러닝 분석과 관련한 여러 이슈들이 대두되면서 개발자들 사이에서는 데이터 처리를 클라우드에서 엣지로 옮기고자 하는 관심들이 생겨나고 있다. 하지만 이를 위해서는 OEM들이 고성능 데이터 프로세싱, 저전력 동작, 소형 폼팩터 특성을 제공하는 엣지 AI 및 머신러닝 추론 솔루션을 활용할 수 있어야 한다.

래티스, 임베디드 비전 및 엣지 AI에 최적화된 CrossLink-NX FPGA 출시5G 커넥티비티, 클라우드 기반 분석, 공장 자동화, 스마트 홈 같은 최신 기술들이 머신러닝을 지원하는 임베디드 비전 솔루션에 대한 수요를 이끌고 있다. 하지만 데이터 지연, 비용, 개인정보 이슈 등 클라우드 기반 머신러닝 분석과 관련한 여러 이슈들이 대두되면서 개발자들 사이에서는 데이터 처리를 클라우드에서 엣지로 옮기고자 하는 관심들이 생겨나고 있다. 하지만 이를 위해서는 OEM들이 고성능 데이터 프로세싱, 저전력 동작, 소형 폼팩터 특성을 제공하는 엣지 AI 및 머신러닝 추론 솔루션을 활용할 수 있어야 한다.- 블로코, ‘2019 블록체인 시장 동향 보고서’ 발표블로코 리포트에 따르면, 블록체인 기술을 가장 많이 도입한 분야는 금융 산업 부분이었다. 금융 산업은 블록체인 기술이 금융업의 주요 역할인 ‘중개와 감시의 기능’을 수행할 수 있어 다양하게 활용된 분야로서, 결제, 블록체인 기술을 활용한 보험, 대출, 자산관리 서비스 등에서 금융 혁신이 이루어지고 있다. 또한 금융사들은 자체적으로 블록체인에 대한 연구를 진행하고 있으며, 변화하는 기술을 각자의 방식으로 적용하여 실행하고 있다

SSD,오펜시브 보안컨퍼런스 ‘타이푼콘(Typhooncon) 2020’ 서울서 개최SSD 시큐어 디스클로저는 비욘드 시큐리티와 협력하여 네트워크, 소프트웨어, 웹 애플리케이션의 보안 취약점을 테스트하고 방어하는 솔루션을 개발하는 글로벌 보안 기업으로, ‘Typhooncon’은 지난 2018년에 홍콩에서 처음 개최된 이후, 2019년인 올해 6월 서울에서 개최되었으며, ‘Typhooncon 2020’도 6월에 서울에서 진행할 예정이다

SSD,오펜시브 보안컨퍼런스 ‘타이푼콘(Typhooncon) 2020’ 서울서 개최SSD 시큐어 디스클로저는 비욘드 시큐리티와 협력하여 네트워크, 소프트웨어, 웹 애플리케이션의 보안 취약점을 테스트하고 방어하는 솔루션을 개발하는 글로벌 보안 기업으로, ‘Typhooncon’은 지난 2018년에 홍콩에서 처음 개최된 이후, 2019년인 올해 6월 서울에서 개최되었으며, ‘Typhooncon 2020’도 6월에 서울에서 진행할 예정이다 인피니언, 뛰어난 성능과 유연성을 제공하는 40nm SLC3x 보안 플랫폼 출시결제, ID 및 기타 애플리케이션을 지원하는 스마트 카드 솔루션이 갈수록 비접촉 다기능 기술로 전환되고 있다. 또한 첨단 생체 인식 기능을 통합하여 사용자 인증을 용이하게 하고 사용자 편의성을 높일 수 있다. 하지만 이러한 새로운 기능을 추가하기 위해서는 다양한 이해 당사자들이 관여해야 하므로 구현이 더 복잡해지고 보안 문제가 까다로워질 수 있다.

인피니언, 뛰어난 성능과 유연성을 제공하는 40nm SLC3x 보안 플랫폼 출시결제, ID 및 기타 애플리케이션을 지원하는 스마트 카드 솔루션이 갈수록 비접촉 다기능 기술로 전환되고 있다. 또한 첨단 생체 인식 기능을 통합하여 사용자 인증을 용이하게 하고 사용자 편의성을 높일 수 있다. 하지만 이러한 새로운 기능을 추가하기 위해서는 다양한 이해 당사자들이 관여해야 하므로 구현이 더 복잡해지고 보안 문제가 까다로워질 수 있다. 한국마이크로소프트, 서피스 프로 7 서피스 랩탑 3 공개서피스를 대표하는 제품으로 꼽히는 서피스 프로는 노트북의 성능과 태블릿 이동성의 완벽한 조화를 이루는 차세대 2-in-1 디바이스로 초경량 디자인에 다재 다능한 성능을 겸비했다. 신제품 서피스 프로 7은 최신 10세대 인텔 코어 프로세서(10th Generation Intel Core processor)를 탑재해 전작인 서피스 프로 6보다 속도가 약 2.3배 빨라졌다.

한국마이크로소프트, 서피스 프로 7 서피스 랩탑 3 공개서피스를 대표하는 제품으로 꼽히는 서피스 프로는 노트북의 성능과 태블릿 이동성의 완벽한 조화를 이루는 차세대 2-in-1 디바이스로 초경량 디자인에 다재 다능한 성능을 겸비했다. 신제품 서피스 프로 7은 최신 10세대 인텔 코어 프로세서(10th Generation Intel Core processor)를 탑재해 전작인 서피스 프로 6보다 속도가 약 2.3배 빨라졌다. 마우저, 미국 내 첨단 물류 시설 주도마우저는 현재 VLM 55대를 보유하고 있으며, 이 중 11대는 신제품이다. 전 세계 제조사 800곳 이상의 공인 유통기업인 마우저는 물류 센터를 확장하고 있으며, 증가하는 고객의 수요를 충족하기 위해 사업 지역도 확장하고 있다. VLM이 완전히 가동되면 한 번에 최대 12만 개의 부품을 실을 수 있어 마우저의 물류팀이 전 세계 63만 명 고객에게 신속하게 주문 상품을 전달하는 데 큰 도움을 준다.

마우저, 미국 내 첨단 물류 시설 주도마우저는 현재 VLM 55대를 보유하고 있으며, 이 중 11대는 신제품이다. 전 세계 제조사 800곳 이상의 공인 유통기업인 마우저는 물류 센터를 확장하고 있으며, 증가하는 고객의 수요를 충족하기 위해 사업 지역도 확장하고 있다. VLM이 완전히 가동되면 한 번에 최대 12만 개의 부품을 실을 수 있어 마우저의 물류팀이 전 세계 63만 명 고객에게 신속하게 주문 상품을 전달하는 데 큰 도움을 준다. 조샌드박스, 자동화된 엔드포인트 멀웨어 심층 분석을 위한 ‘카본블랙 커넥터’ 출시카본블랙 사용자들은 이 커넥터를 사용하여 조샌드박스로 자동화된 멀웨어 심층 분석을 실시할 수 있다. 카본블랙에서 탐지된 의심스러운 파일이 커넥터를 통해 조샌드박스로 전송되어 심층 분석 후, 생성된 위협 인텔리전스 데이터를 카본블랙으로 다시 내보내기 할 수 있다.

조샌드박스, 자동화된 엔드포인트 멀웨어 심층 분석을 위한 ‘카본블랙 커넥터’ 출시카본블랙 사용자들은 이 커넥터를 사용하여 조샌드박스로 자동화된 멀웨어 심층 분석을 실시할 수 있다. 카본블랙에서 탐지된 의심스러운 파일이 커넥터를 통해 조샌드박스로 전송되어 심층 분석 후, 생성된 위협 인텔리전스 데이터를 카본블랙으로 다시 내보내기 할 수 있다.

인텔 파운드리, 고개구율 극자외선(High-NA EUV) 도입으로 칩 제조 분야 선도

인텔 파운드리, 고개구율 극자외선(High-NA EUV) 도입으로 칩 제조 분야 선도 NXP, 연간 기업 지속 가능성 보고서 - ESG 목표 달성 현황 공개

NXP, 연간 기업 지속 가능성 보고서 - ESG 목표 달성 현황 공개 로데슈바르즈, 획기적인 성능으로 무장한 R&S NGC100 파워 서플라이 제품군 신규 출시

로데슈바르즈, 획기적인 성능으로 무장한 R&S NGC100 파워 서플라이 제품군 신규 출시 IMDT와 Hailo가 합작하여 최고의 실시간 성능을 위한 엣지 AI 솔루션 출시

IMDT와 Hailo가 합작하여 최고의 실시간 성능을 위한 엣지 AI 솔루션 출시 콩가텍, 인텔 코어 i3 및 인텔 아톰 x7000RE 프로세서 탑재 SMARC 모듈 출시

콩가텍, 인텔 코어 i3 및 인텔 아톰 x7000RE 프로세서 탑재 SMARC 모듈 출시

- 인텔, 세계 최대규모 뉴로모픽 시스템 공개

- 마이크로칩, 항공기 전기화 전화를 간소화하는 통합 구동 파워 솔루션 출시

- 텔레다인르크로이, 광범위한 통신 기술 데이터를 원활하게 포착하는 프론트라인 X500e 출시

- TTTech Auto, 복잡한 소프트웨어 통합을 혁신할 차세대 스케줄러 ‘MotionWise Schedule’ 출시

- 아이스아이, 글로벌 SAR 리더십 확장을 위한 기업의 성장 펀딩 라운드 초과 달성

- 오나인솔루션즈, 생성형 AI 기술 적용해 ‘o9 Digital Brain’ 플랫폼 강화

그래픽 / 영상

결정론, 새로운 이더넷 애플리케이션을 열다

결정론, 새로운 이더넷 애플리케이션을 열다 AMD, 새로운 2세대 버설 적응형 SoC로 AI 기반 임베디드 시스템의 종단간 가속 지원

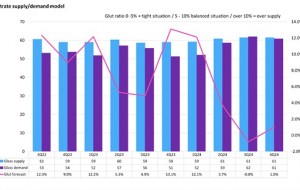

AMD, 새로운 2세대 버설 적응형 SoC로 AI 기반 임베디드 시스템의 종단간 가속 지원 2024년, 디스플레이 글래스 산업 공급부족 우려

2024년, 디스플레이 글래스 산업 공급부족 우려

많이 본 뉴스

AMD의 스파르탄 울트라스케일+, 비용 최적화 FPGA의 새로운 시대를 열다

AMD의 스파르탄 울트라스케일+, 비용 최적화 FPGA의 새로운 시대를 열다 인텔, AI 애플리케이션 확장할 새로운 ‘엣지 플랫폼’ 발표

인텔, AI 애플리케이션 확장할 새로운 ‘엣지 플랫폼’ 발표 버티브, 수요 증가에 대비해 2025년까지 글로벌 생산 능력 두 배 확장

버티브, 수요 증가에 대비해 2025년까지 글로벌 생산 능력 두 배 확장 삼텍, DC~67GHz의 좁은 바디 RF 에지 론치 커넥터 출시

삼텍, DC~67GHz의 좁은 바디 RF 에지 론치 커넥터 출시 시놀로지, DISS 2024 컨퍼런스에서 데이터 보안 관리 솔루션 선보여

시놀로지, DISS 2024 컨퍼런스에서 데이터 보안 관리 솔루션 선보여 두산디지털이노베이션, 3년 연속 SAP 최우수 파트너상 수상

두산디지털이노베이션, 3년 연속 SAP 최우수 파트너상 수상 로옴의 EcoGaN, 이너지(Innergie)의 45W 출력 AC 어댑터에 채택

로옴의 EcoGaN, 이너지(Innergie)의 45W 출력 AC 어댑터에 채택 엔비디아 타오 툴킷과 NXP 엣지 디바이스 통합으로 AI 배포 가속

엔비디아 타오 툴킷과 NXP 엣지 디바이스 통합으로 AI 배포 가속 KT, 5G와 위성 상용 주파수 지원하는 RIS 기술 개발

KT, 5G와 위성 상용 주파수 지원하는 RIS 기술 개발 엔비디아, 새로운 컴퓨팅 시대를 여는 블랙웰 플랫폼 출시

엔비디아, 새로운 컴퓨팅 시대를 여는 블랙웰 플랫폼 출시